半導(dǎo)體集成電路的發(fā)展及封裝工藝面臨的挑戰(zhàn)

半導(dǎo)體芯片結(jié)構(gòu)尺寸的縮小使得RC延遲成為制約集成電路性能進(jìn)一步提高的關(guān)鍵性因素。轉(zhuǎn)向低k銅工藝技術(shù)是業(yè)界給出的解決方案。雙大馬士革工藝取代了傳統(tǒng)的鋁“減”工藝,成為低k銅互連材料的標(biāo)準(zhǔn)制造工藝。

本文引用地址:http://www.104case.com/article/84972.htm為了能與芯片制造工藝完美結(jié)合,不產(chǎn)生可靠性問(wèn)題,低k絕緣材料必須具備一系列期望的材料特性,對(duì)低k材料研發(fā)本身的挑戰(zhàn)在于:在獲得所需要的低介電常數(shù)的同時(shí),低k材料還必須滿足良好的熱和機(jī)械特性。但目前并沒(méi)有完全符合這些期望特性的低k材料被制造出來(lái),因而給半導(dǎo)體制造工藝帶來(lái)了挑戰(zhàn)。

由于低k材料本身的材料特性(與金屬層較弱的粘結(jié)力,較弱的機(jī)械強(qiáng)度),在晶片的切割時(shí)在芯片的邊緣會(huì)出現(xiàn)嚴(yán)重的金屬層與ILD層的分層或剝離;在焊線過(guò)程中會(huì)出現(xiàn)斷焊,弱焊或金屬層與ILD層的剝離。金鋁兩種材料的焊接在可靠性測(cè)試中出現(xiàn)比非低k材料焊線嚴(yán)重的金屬間化合物的分層,導(dǎo)致集成電路電性失效。上述這些可制造性及可靠性的問(wèn)題構(gòu)成了對(duì)半導(dǎo)體封裝工藝的挑戰(zhàn)。

1 半導(dǎo)體集成電路的發(fā)展趨勢(shì)

高速度,低成本和高可靠性代表了終端用戶對(duì)半導(dǎo)體集成電路發(fā)展/改進(jìn)的期望。而支持半導(dǎo)體集成電路不斷改進(jìn)的原動(dòng)力是芯片關(guān)鍵尺寸的不斷縮小。半導(dǎo)體集成電路制造產(chǎn)業(yè)已經(jīng)成為電子制造業(yè)的基礎(chǔ)和核心,支持并推動(dòng)著相關(guān)產(chǎn)業(yè)的繁榮與發(fā)展。半導(dǎo)體工業(yè)協(xié)會(huì)(SIA Semiconductor Industry Association)在2007年2月2日的世界半導(dǎo)體集成電路銷售調(diào)查報(bào)告中提到“全球半導(dǎo)體集成電路的銷售額在2006年又創(chuàng)新高,達(dá)到2477 億美元,比2005年的2275億美元的銷售額提高了8.9%。2006年是消費(fèi)類半導(dǎo)體年,半導(dǎo)體集成電路銷售額的增長(zhǎng)主要來(lái)自流行的消費(fèi)類產(chǎn)品,如手機(jī),MP3播放器及高清電視等。而這些電子產(chǎn)品銷售額的增長(zhǎng)應(yīng)歸功于半導(dǎo)體集成電路設(shè)計(jì)/制造技術(shù)的進(jìn)步以及隨之而來(lái)的功能更豐富,成本更低廉的半導(dǎo)體集成電路的問(wèn)世。

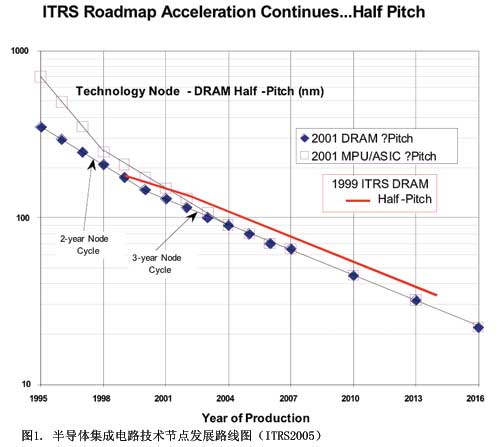

國(guó)際半導(dǎo)體技術(shù)發(fā)展路線圖(ITRS International Technology Roadmap for Semiconductor)是由SIA出版的預(yù)測(cè)全球半導(dǎo)體集成電路技術(shù)發(fā)展的權(quán)威性報(bào)告[1]。 ITRS報(bào)告每?jī)赡旮乱淮危瑘D1是ITRS 2005年版報(bào)告中關(guān)于DRAM和MPU技術(shù)節(jié)點(diǎn)(Technology Node)的發(fā)展趨勢(shì)的預(yù)測(cè)。從圖中可以看出,DRAM 線間距 (Half Pitch)從2001年以后,每3年改變一個(gè)技術(shù)節(jié)點(diǎn),每?jī)蓚€(gè)技術(shù)節(jié)點(diǎn),線間距降低50%。而在2001年以前,這個(gè)技術(shù)指標(biāo)每?jī)赡昃透淖円粋€(gè)技術(shù)節(jié)點(diǎn)。MPU / ASIC的1/2 線間距一直到2004年還維持著每隔2年改變一個(gè)技術(shù)節(jié)點(diǎn)的能力,但在2004年以后,MPU / ASIC進(jìn)步的節(jié)奏也慢了下來(lái),變?yōu)槊?年改變一個(gè)技術(shù)節(jié)點(diǎn),與DRAM的發(fā)展趨勢(shì)同步。

圖1半導(dǎo)體集成電路技術(shù)節(jié)點(diǎn)發(fā)展路線圖

表1列出了對(duì)光刻技術(shù)的需求的時(shí)間路線圖,從表中也可以看出,MPU的物理柵極長(zhǎng)度(Ph GL)自2005年以后也從每2年一個(gè)變化周期改為每3年一個(gè)變化周期,與DRAM/ MPU 1/2 線間距的變化趨勢(shì)同步。

表1半導(dǎo)體集成電路光刻技術(shù)發(fā)展路線圖

2 半導(dǎo)體集成電路發(fā)展的瓶頸和解決方案

集成電路元器件密度與能力的不斷提高是以集成電路關(guān)鍵尺寸的不斷縮小和芯片內(nèi)信號(hào)互連布線不斷復(fù)雜化,布線層數(shù)不斷增加為代價(jià)的[2-3]。當(dāng)集成電路的關(guān)鍵尺寸降到90納米以下時(shí),信號(hào)傳輸延遲,交互干擾噪聲已及互連線的功率消耗等問(wèn)題已成為甚大規(guī)模集成電路(ULSI)發(fā)展的阻礙。互連線尺寸因素對(duì)集成電路性能的影響可以通過(guò)對(duì)多層互連線阻容信號(hào)延遲 (RC Delay)的分析獲得[4]。

假設(shè)集成電路內(nèi)信號(hào)互連線的材料保持不變,則隨著互連線尺寸的不斷收縮,RC延遲將以互連線尺寸收縮速率的平方關(guān)系增加。在90nm技術(shù)節(jié)點(diǎn),由互連導(dǎo)致的信號(hào)延遲已經(jīng)超過(guò)了微處理器的門延遲。如果再考慮到交互干擾噪聲,功率消耗問(wèn)題,集成電路的整體性能會(huì)進(jìn)一步下降。同時(shí),由于器件集成度的提高,互連金屬線的層數(shù)也要相應(yīng)地增加,集成電路制造工藝的復(fù)雜化將會(huì)對(duì)制造良品率和制造成本產(chǎn)生負(fù)面影響。

為了解決上述問(wèn)題,具有更低電阻率的互連金屬材料和較低介電常數(shù)的層間絕緣材料被開(kāi)發(fā)出來(lái)。IBM公司于1997年率先宣布低介電常數(shù)銅工藝晶片制造技術(shù)開(kāi)發(fā)成功。銅金屬具有比鋁金屬更低的電阻率(1.68μΩ.cm vs 2.65μΩ.cm),采用銅金屬互連線不僅可以降低互連線的線寬,還可以降低互連線的厚度,而后者可以有效地降低同一層中互連線之間的電容,減小交互干擾噪聲和電源功率消耗。銅互連導(dǎo)線與較低K值的層間絕緣材料的引進(jìn),有效地解決了RC延遲的問(wèn)題[5]。

3 低k銅工藝對(duì)半導(dǎo)體封裝工藝的挑戰(zhàn)

在半導(dǎo)體集成電路的制造工藝中引入低介電材料和銅導(dǎo)線能夠顯著地提高集成電路的性能,但同時(shí)它也為后續(xù)的半導(dǎo)體封裝工藝帶來(lái)了諸多困難。當(dāng)作為金屬層間絕緣材料的二氧化硅被低介電材料(K值小于3)所取代時(shí),新的ILD層比傳統(tǒng)的ILD層更脆,而且具有相對(duì)較差的導(dǎo)熱性和機(jī)械強(qiáng)度,與金屬層的粘結(jié)力與傳統(tǒng)的二氧化硅材料相比較小。低k材料的引入給半導(dǎo)體封裝中的劃片(Dicing Saw)和焊線(Wire Bonding)工藝帶來(lái)了挑戰(zhàn)[6]。

4 在劃片工藝中金屬層與ILD層的分層與剝離

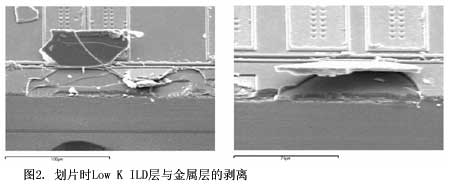

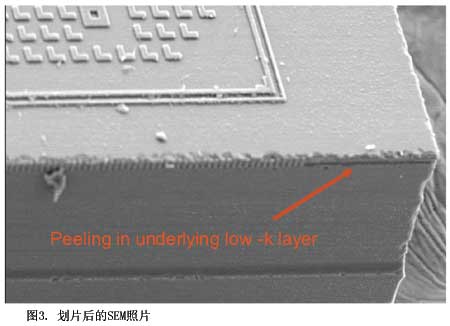

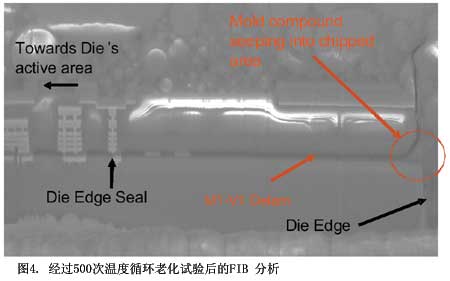

在低k 晶片的劃片過(guò)程中,最常見(jiàn)的缺陷是芯片邊緣金屬層和ILD層的分層(Delamination)或剝離(Peeling)。由于低k材料本身所固有的特性(如與金屬層較弱的粘結(jié)力,較弱的機(jī)械強(qiáng)度),在低k晶片的劃片過(guò)程中,經(jīng)常可以在芯片邊緣發(fā)現(xiàn)嚴(yán)重的金屬層與ILD層的分層甚至是剝離(如圖2,3所示)。這種缺陷在普通的非低k晶片的劃片過(guò)程中是不存在的或是極少出現(xiàn)的。這種新的缺陷不僅降低了劃片工序的良品率,更嚴(yán)重的是它會(huì)使集成電路在使用過(guò)程中產(chǎn)生潛在的可靠性問(wèn)題(圖4)。而在集成電路半導(dǎo)體封裝的大規(guī)模生產(chǎn)中,對(duì)每一個(gè)芯片的切割質(zhì)量進(jìn)行100%

的質(zhì)量檢查是不可能做到的,因?yàn)槭軝z測(cè)手段和檢測(cè)時(shí)間的限制,100%的質(zhì)量檢查無(wú)法滿足經(jīng)濟(jì)規(guī)模生產(chǎn)的要求。同時(shí),依靠生產(chǎn)檢查人員對(duì)已劃片的芯片樣品進(jìn)行的抽檢又不能保證發(fā)現(xiàn)所有的切割缺陷。因?yàn)槿鄙賹?duì)低k晶片切割缺陷的深入理解及其與封裝可靠性的關(guān)聯(lián)性,以及切割缺陷在晶片上的分布規(guī)律,使得低k晶片的切割工藝的可制造性受到了關(guān)注[7]。

圖2劃片時(shí)LowKILD層與金屬層的剝離

圖3劃片后的SEM照片

圖4經(jīng)過(guò)500次溫度循環(huán)老化試驗(yàn)后的FIB分析

這種分層或剝離在芯片隨后的使用過(guò)程中或可靠性試驗(yàn)中,隨著工況條件的惡化而擴(kuò)散,直至斷裂,導(dǎo)致集成電路的失效。

萬(wàn)能遙控器相關(guān)文章:萬(wàn)能遙控器代碼

電路相關(guān)文章:電路分析基礎(chǔ)

pic相關(guān)文章:pic是什么

評(píng)論