芯片,遇到難題

近,semiengineering 的文章指出,由于復(fù)雜性不斷上升,芯片制造從單片芯片轉(zhuǎn)向多芯片組件,需要進(jìn)行更多次迭代,以及定制化程度不斷提高導(dǎo)致設(shè)計(jì)和驗(yàn)證更加耗時(shí),首次流片的成功率正在急劇下降。

本文引用地址:http://www.104case.com/article/202505/470482.htm從西門子提供的數(shù)據(jù)看,半導(dǎo)體行業(yè)首次流片的成功率已經(jīng)達(dá)到了歷史低點(diǎn)。此外,隨著 2nm 的到來,先進(jìn)制程工藝下的芯片良率也很難提高。

芯片遇到了大難題。

芯片流片成功率,歷史低點(diǎn)

流片對于芯片設(shè)計(jì)來說,就是參加一次大考。

流片是檢驗(yàn)芯片設(shè)計(jì)是否成功的關(guān)鍵,就是將設(shè)計(jì)好的方案交給代工廠生產(chǎn)出樣品,檢驗(yàn)設(shè)計(jì)的芯片有沒有達(dá)到設(shè)計(jì)要求,或者要不要進(jìn)一步優(yōu)化。如果能夠生產(chǎn)出符合要求的芯片,那么就可以大規(guī)模生產(chǎn)了。

在紀(jì)錄片《電子立國自述傳》中,對于流片時(shí)的心情是這么描述的:每次芯片 tapeout 的兩三個(gè)月里,我的內(nèi)心終日惶惶不安,難以入眠。無時(shí)無刻不在想哪里對不對,會不會有問題……等到芯片送回來,第一次按 RESET 時(shí),我的心情緊張到了極點(diǎn),松開 RESET 的瞬間,便是區(qū)分天堂與地獄的瞬間。

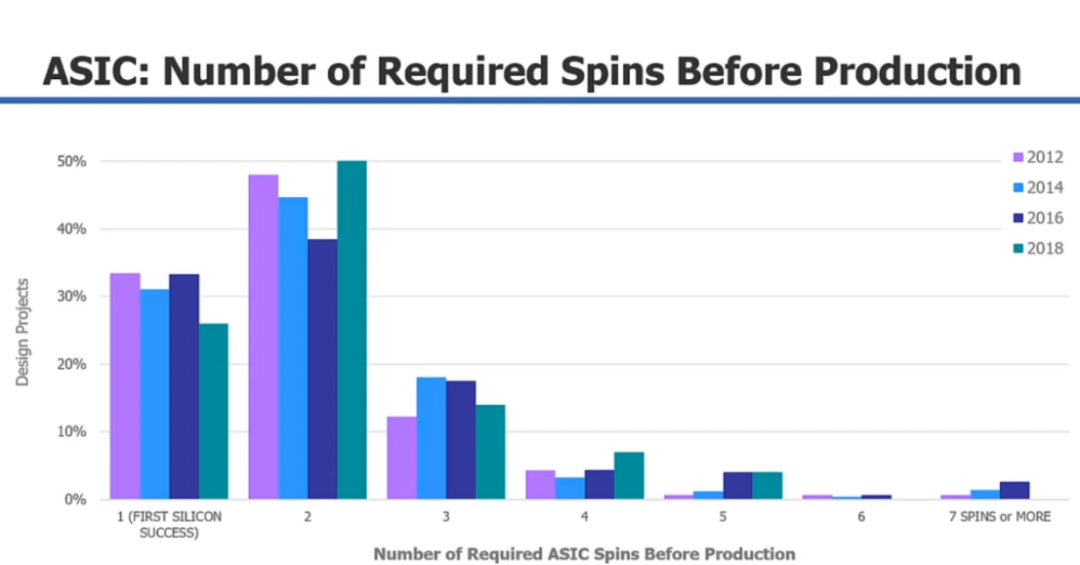

從西門子的數(shù)據(jù)來看,正常芯片流片首次成功率在30% 左右,但兩年降到 24%,2025 年成功率更是降低至 14%,十家中有八家都會失敗。

有些芯片失敗是因?yàn)樵O(shè)計(jì)流程過于隨意,有的芯片失敗不一定是因?yàn)楣δ軉栴}。如果流片返回后運(yùn)行速度比預(yù)期慢 10%,或者功耗比預(yù)期大 10%,在市場上可能就沒有競爭力了,也就需要重新流片。

不少芯片巨頭都在流片上栽過跟頭,比如 AMD 的 Bulldozer(推土機(jī))架構(gòu)芯片、高通驍龍 810 芯片等。

AMD 的 Bulldozer 架構(gòu)于 2007 年開始研發(fā),將兩個(gè)物理核心組成一個(gè)模塊,共享浮點(diǎn)單元和 L2 緩存,但實(shí)際性能未達(dá)預(yù)期。由于設(shè)計(jì)復(fù)雜,流片后性能不佳,前期研發(fā)費(fèi)用浪費(fèi),而英特爾同期推出的 Sandy Bridge 架構(gòu)處理器性能更優(yōu),搶占了市場份額。

高通驍龍810 芯片是 2015 年推出的旗艦移動處理器,但因采用先進(jìn)制程和高性能設(shè)計(jì),流片后出現(xiàn)嚴(yán)重發(fā)熱和高功耗問題,導(dǎo)致手機(jī)過熱、降頻,用戶體驗(yàn)差。高通隨后進(jìn)行了改進(jìn)優(yōu)化,而競爭對手三星則憑借更穩(wěn)定、低功耗的 Exynos 處理器搶占了部分市場份額。

流片成功率下降,主要有四個(gè)原因。

一是,芯片越來越復(fù)雜。現(xiàn)在的芯片設(shè)計(jì)越來越多地采用多芯片組件,這些不同組件往往需要在不同的工藝節(jié)點(diǎn)生產(chǎn)。以先進(jìn)的服務(wù)器芯片為例,計(jì)算核心采用 5nm 工藝以實(shí)現(xiàn)更高性能和更低功耗,而存儲單元可能使用更成熟的 14nm 工藝以保證成本和穩(wěn)定性。這意味著需要協(xié)調(diào)多個(gè)代工廠和工藝技術(shù),增加了設(shè)計(jì)和制造的復(fù)雜性。

二是,定制化芯片越來越多。定制化芯片是針對特定的數(shù)據(jù)類型、算法或應(yīng)用場景設(shè)計(jì),這使得芯片設(shè)計(jì)和驗(yàn)證工作變得異常繁瑣。例如,用于深度學(xué)習(xí)推理的定制芯片,需要針對神經(jīng)網(wǎng)絡(luò)的特定結(jié)構(gòu)和計(jì)算模式進(jìn)行優(yōu)化,從架構(gòu)設(shè)計(jì)到指令集開發(fā)都需要重新規(guī)劃。

三是,企業(yè)開發(fā)模式變了。過去,芯片開發(fā)周期通常為 18 個(gè)月左右,而現(xiàn)在企業(yè)為了保持市場競爭力,需要在更短的時(shí)間內(nèi)推出更多產(chǎn)品。許多芯片企業(yè)為了按時(shí)完成流片任務(wù),不得不壓縮設(shè)計(jì)和驗(yàn)證時(shí)間,甚至在一些關(guān)鍵環(huán)節(jié)簡化流程。設(shè)計(jì)中的潛在問題無法被及時(shí)發(fā)現(xiàn)和解決,增加了流片失敗的風(fēng)險(xiǎn)。

四是,人工智能帶來的壓力。人工智能的快速發(fā)展對半導(dǎo)體芯片的計(jì)算能力提出了極高的要求。AI 應(yīng)用需要芯片提供更高的算力,但目前的開發(fā)和驗(yàn)證生產(chǎn)力并未有相應(yīng)的突破。這導(dǎo)致芯片設(shè)計(jì)團(tuán)隊(duì)在有限的時(shí)間內(nèi)需要交付更復(fù)雜的設(shè)計(jì),增加了首次流片失敗的風(fēng)險(xiǎn)。

半導(dǎo)體工程的編輯 Brian Bailey 在分析首次流片成功率降低的原因時(shí)也表示:「人工智能對芯片算力需求暴增,遠(yuǎn)超當(dāng)前半導(dǎo)體技術(shù)和架構(gòu)的進(jìn)步速度。但開發(fā)和驗(yàn)證技術(shù)卻沒跟上,工程師只能用老工具,在更短時(shí)間內(nèi)完成更多工作,流片失敗也就不奇怪了。」

上一次出現(xiàn)流片成功率降低還是在 2018 年。

在 2018 年之前,半導(dǎo)體行業(yè)的 ASIC 首次流片成功率也是維持在 30% 左右,但 2018 年直接降到了 26%。FPGA 的數(shù)據(jù)比較難統(tǒng)計(jì),但是可以看生產(chǎn)中漏掉的 BUG 數(shù)量。2018 年,只有 16% 的 FPGA 項(xiàng)目能夠?qū)崿F(xiàn)零 BUG 漏出,這其實(shí)比 ASIC 首次流片成功率的下降更加嚴(yán)重。

成功率下降的節(jié)點(diǎn),正是業(yè)內(nèi)大量設(shè)計(jì)從 28nm 遷移到 14nm 的時(shí)候,并且 7nm 當(dāng)時(shí)還在逐漸普及。并且,越來越多的芯片設(shè)計(jì)把安全當(dāng)作一個(gè)關(guān)鍵因素,汽車和工業(yè)領(lǐng)域尤為突出。

芯片良率,難倒巨頭

在芯片行業(yè)面臨流片成功率暴跌的嚴(yán)峻形勢下,即便成功完成流片,也并非萬事大吉。流片只是芯片生產(chǎn)的開端,后續(xù)生產(chǎn)環(huán)節(jié)同樣挑戰(zhàn)重重,其中芯片良率低的問題同樣棘手,成為制約芯片行業(yè)發(fā)展的又一大阻礙。

良率是半導(dǎo)體工廠的核心競爭力所在,也被稱為是半導(dǎo)體工廠的「生命線」。

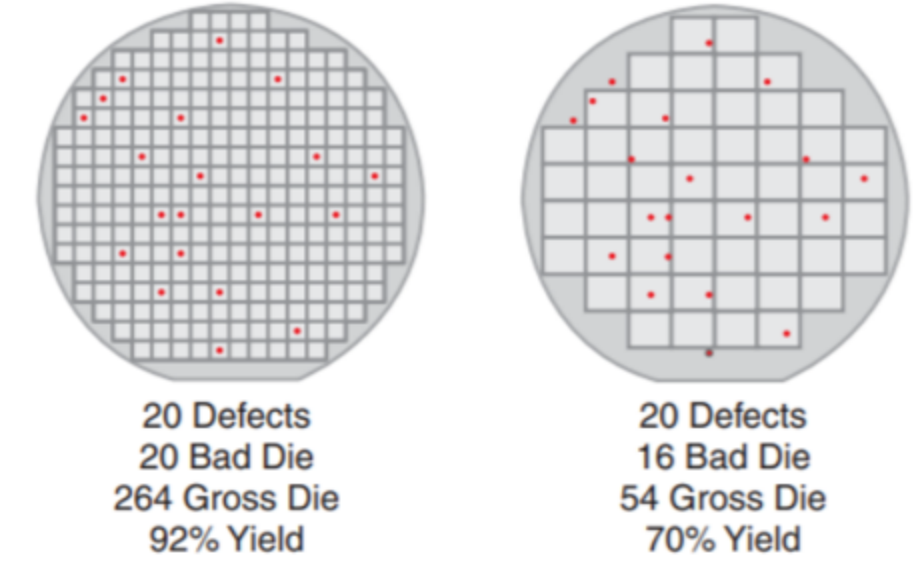

芯片良率,指合格芯片的數(shù)量與生產(chǎn)出的總芯片數(shù)量的比例。即:良率=合格芯片數(shù)量/生產(chǎn)的芯片總量 x 100%

例如,如果在一片晶圓上制造了 1000 個(gè)芯片,其中 950 個(gè)是合格的,那么良率就是:良率=(950/1000)×100%=95%

良率通常需要在整個(gè)生產(chǎn)過程中進(jìn)行多個(gè)階段的測量和計(jì)算,因?yàn)槊總€(gè)生產(chǎn)步驟都有可能引入缺陷,影響最終的良率。通常相應(yīng)芯片良率需要達(dá)到 70% 或更高才能進(jìn)入大規(guī)模量產(chǎn)階段。

在行業(yè)內(nèi),即便強(qiáng)如臺積電、三星、英特爾這些巨頭,也被芯片良率問題所困擾。

臺積電在先進(jìn)制程良率控制上表現(xiàn)較為出色。在 2020 年時(shí),臺積電在 IEEE IEDM 會議上披露,其5 納米工藝的測試芯片平均良率為 80%,峰值良率超過 90%。

據(jù) MSN 報(bào)道,臺積電3 納米芯片良率高達(dá) 80% 以上。市場上的巨頭如蘋果、高通也都紛紛選擇了臺積電 3nm。

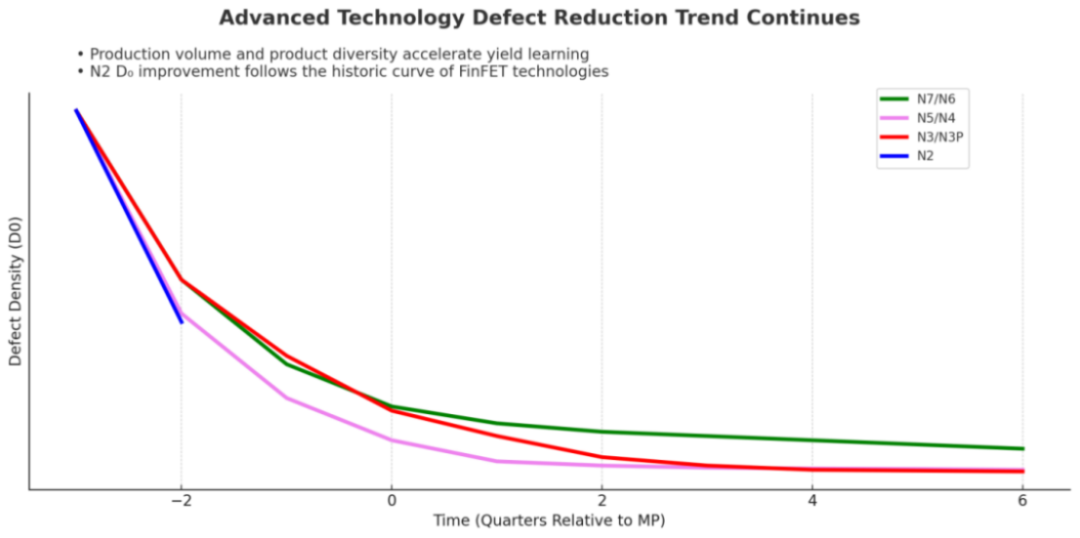

臺積電 2nm 的信號比較積極。據(jù)了解,2nm 制程技術(shù)在成熟度上取得了快速進(jìn)展,其缺陷密度率已與 3nm 和 5nm 相當(dāng),并采用了新的環(huán)繞柵極晶體管(GAAFET)架構(gòu)。與 3nm 增強(qiáng)版(N3E)相比,2nm 制程的速度提升了 10% 至 15%。目前,臺積電的2nm 制程的良率已達(dá)到 60% 以上。

相比之下,三星的情況則不容樂觀。2nm 工藝良率從年初的 20% - 30% 提升至 40% 以上,其首款采用 2 納米工藝的 Exynos 2600 芯片計(jì)劃于 2025 年 11 月量產(chǎn)。這與前文提到的臺積電 60% 的良率,還有差距。

3nm 工藝問題更為突出。SF3E-3GAE(第一代 3nm GAA 工藝)的良率在 50%~60% 之間,未達(dá)到最初設(shè)定的 70% 目標(biāo)。SF3-3GAP(第二代 3nm GAA 工藝)良率更低,僅為 20% 左右,遠(yuǎn)低于預(yù)期目標(biāo),導(dǎo)致三星在 3nm 芯片代工市場競爭力不足,甚至自家的 Exynos 2500 芯片也因良率問題難產(chǎn)。

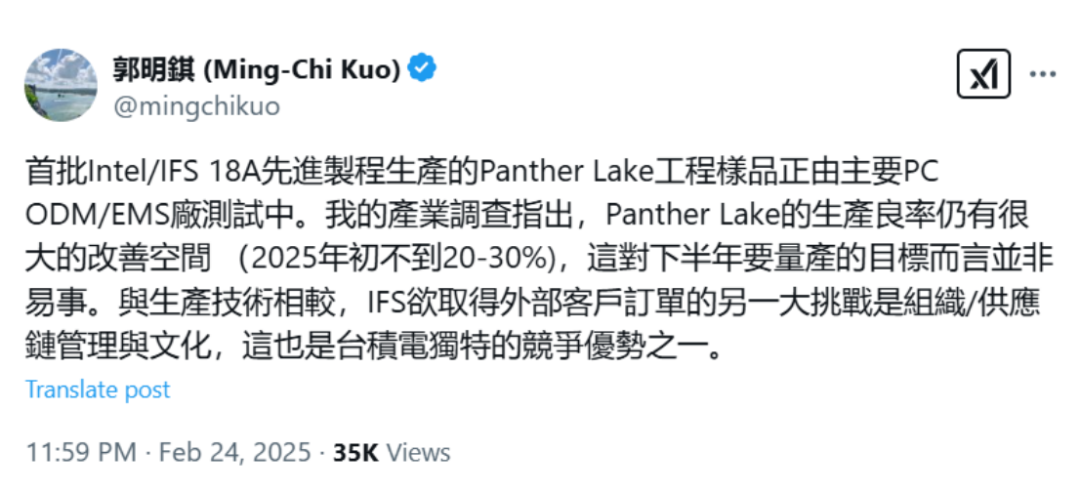

英特爾在良率數(shù)據(jù)披露上較為模糊,雖有副總裁表示 Intel 4 制程良率高于預(yù)期,Intel 3 制程達(dá)成整體良率和性能目標(biāo),但天風(fēng)國際分析師郭明錤曾稱,2025 年初首批 Intel/IFS 18A 先進(jìn)制程生產(chǎn)的 Panther Lake 工程樣品良率不到 20% - 30%。

不過這一說法遭到英特爾方面駁斥。英特爾投資者關(guān)系副總裁 John Pitzer 在摩根士丹利科技、媒體和電信會議上表示:「總體而言,我們認(rèn)為 Intel 18A 的水平能夠?qū)?biāo)臺積電的 N3 或者 N2。我們正按計(jì)劃推進(jìn) Intel 18A,并已宣布將在今年上半年完成首個(gè)外部客戶的流片工作。」

巨頭們在芯片良率上的困境,足見這一難題的棘手程度。

良率提不上去,原因是多方面的。

原材料上,硅片質(zhì)量、光刻膠均勻度、摻雜劑精度等都會影響良率,比如硅片有雜質(zhì)、光刻膠不均勻,都會導(dǎo)致芯片性能出問題,而高質(zhì)量原材料不僅技術(shù)要求高,價(jià)格也貴。

制造環(huán)境和設(shè)備也很關(guān)鍵,芯片生產(chǎn)需要超潔凈環(huán)境,空氣中的顆粒都可能造成芯片缺陷,設(shè)備的穩(wěn)定性、精度和維護(hù)也很重要,引入新設(shè)備成本高,還可能存在技術(shù)適配問題。工藝技術(shù)上,光刻、蝕刻等流程復(fù)雜,現(xiàn)有工藝優(yōu)化空間有限,新技術(shù)如極紫外光刻(EUV)又面臨技術(shù)和成本難題。

此外,質(zhì)量管控不到位,生產(chǎn)過程中數(shù)據(jù)收集和分析不及時(shí),就沒法提前發(fā)現(xiàn)和解決問題,導(dǎo)致缺陷難以糾正。

結(jié)語

芯片流片成功率暴跌和良率提升困難,是當(dāng)前芯片行業(yè)必須面對的挑戰(zhàn)。

提高流片成功率,要優(yōu)化設(shè)計(jì),可以用 AI 輔助設(shè)計(jì),提高準(zhǔn)確性;加強(qiáng)設(shè)計(jì)驗(yàn)證,提前發(fā)現(xiàn)問題。還要重視人才培養(yǎng),提升工程師的專業(yè)能力。同時(shí),芯片設(shè)計(jì)企業(yè)要和晶圓代工廠、EDA 供應(yīng)商加強(qiáng)合作,整合產(chǎn)業(yè)鏈資源。

提升芯片良率,要改良制程,優(yōu)化設(shè)計(jì)和工藝控制。在設(shè)備和材料上,升級設(shè)備、選用優(yōu)質(zhì)原材料。技術(shù)創(chuàng)新也很重要,利用 AI 和大數(shù)據(jù)監(jiān)控生產(chǎn)線,探索新材料、新工藝。還要建立嚴(yán)格的質(zhì)量管控體系,從原材料采購到成品全流程監(jiān)控。

這些問題的解決,需要各方從技術(shù)、人才、產(chǎn)業(yè)鏈等多方面努力。

評論