解析半導體工藝節(jié)點的演進 尋找摩爾定律的曙光

01 摩爾定律下的工藝節(jié)點的形成

本文引用地址:http://www.104case.com/article/201707/362299.htm1958年,美國德州儀器公司的工程師杰克·基爾比制成了世界上第一片集成電路,1962年,德州儀器公司建成世界上第一條商業(yè)化集成電路生產(chǎn)線。此后,在市場需求的驅(qū)動下,集成電路發(fā)展成為一個龐大的產(chǎn)業(yè),從小規(guī)模集成電路(SSI)到中規(guī)模集成電路(MSI)、再到大規(guī)模集成電路(LSI),一直到現(xiàn)在的超大規(guī)模集成電路(VLSI)。集成度被看作是描述集成電路工藝先進程度的一個重要指標,通常用晶體管數(shù)目來表示集成度高低,一個芯片里含有的晶體管數(shù)目越多,芯片的功能也就越強。因此,集成電路的規(guī)模反映了集成電路的先進程度。

集成度的提高,不僅意味著單個晶體管的尺寸縮小了,同時也意味著采用了更加先進的制造工藝,因為晶體管尺寸與制造工藝之間有著密切的聯(lián)系。可以說,集成電路技術(shù)的發(fā)展過程,就是把晶體管尺寸做得越來越小的過程。九十年代的大規(guī)模集成電路普遍采用的是微米級工藝,筆者在上世紀90年代初做設計時就是采用5微米和3微米標準單元庫,這也是那個年代的主流工藝(晶圓尺寸是3英寸和4英寸)。二十多年過去了,現(xiàn)在已經(jīng)發(fā)展到納米級工藝了,中芯國際去年實現(xiàn)量產(chǎn)的28納米工藝,比起3微米工藝,尺寸縮小了100多倍。

這些工藝演進的背后,是更多金錢的投入。因為更小的尺寸意味著對設計和制造設備以及芯片材料等都有更為苛刻的要求,為了克服技術(shù)門檻,芯片企業(yè)每年需要投入數(shù)億、數(shù)十億美元的研發(fā)經(jīng)費,不知有多少世界一流的科學家和工程師都參與了這一耗資巨大的芯片微縮化工程。

那么5微米、3微米、以及90納米、28納米等等這些“節(jié)點”是怎樣形成的呢?可以說這是描述摩爾定律進程的一個指標。摩爾定律說,半導體芯片每一年半(后來改為兩年),其集成度翻一番,并伴隨著性能的增長和成本的下降。怎樣描述這個集成度呢?這就有了工藝“節(jié)點”的說法。即工藝節(jié)點數(shù)值越小,表征芯片的集成度就越高。這些數(shù)值也被《國際半導體技術(shù)藍圖(ITRS)》用來劃分半導體工藝的階段(也稱工藝代),或描述芯片的先進性。

這里有必要解釋這些數(shù)值表示的是什么尺寸。例如28nm工藝,這里的28nm是指晶體管柵極的最小線寬(柵寬)。實際設計中除了柵極,其他的設計尺寸一般都大于工藝節(jié)點的尺寸,例如晶體管之間的金屬連線寬度、有源區(qū)寬度等。

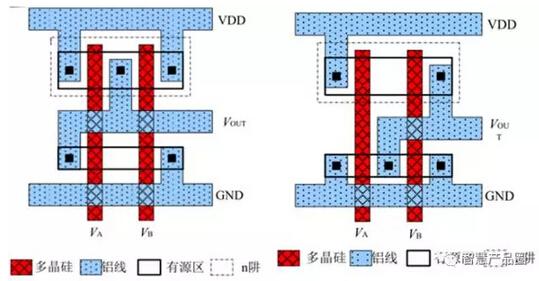

▲ 圖一 與非門、或門的版圖

圖一是個例子。在這個與非門和或非門的版圖里,白的是襯底層,紅的是多晶硅層,藍的是金屬層。這其中只有紅的多晶硅柵極的最小線寬是可以達到28nm的,其他一切尺寸都是要大于28nm。具體各層線寬的最小值需要看該工藝的設計規(guī)則(Design Rull)。

為什么用柵極線寬而不是其他的線寬來表征工藝節(jié)點,這是因為柵極寬度一般是整個設計中最重要的參數(shù)。在CMOS電路中,MOS晶體管最主要的功能就是通過柵極控制源漏之間的電流。這個電流受很多因素影響,例如晶體管遷移率、絕緣層電容,還有各種效應等,這些都與半導體工藝有關,工藝定了設計很難改變。一般情況下唯一可以設計的參數(shù)就是溝道寬長比,溝道寬長比就是晶體管柵極的長寬比(長溝器件可以直接近似,短溝器件要加修正項)。也就是說在電壓一樣的情況下,柵極越寬,溝道就越長,源漏電流就越小。

所以在設計中,溝道越短,意味著晶體管的尺寸越小,單位面積可以存放的晶體管數(shù)量就越多,芯片集成度就越高;換一種說法是設計出來的芯片面積就越小,芯片的價格就越便宜。當然這是在只考慮生產(chǎn)成本,不考慮NRE費用的前提下。

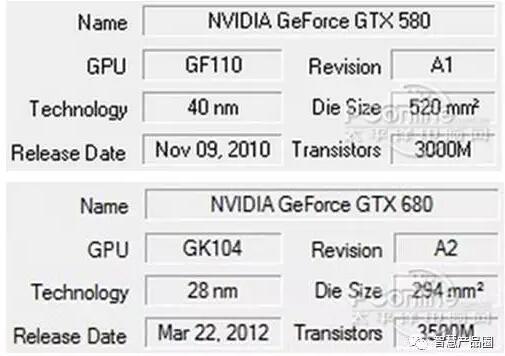

▲ 圖二 NVIDIA GTX580(40nm工藝) 與 GTX680(28nm工藝)的對比

從圖二,我們看到Geforce GTX 680雖然晶體管數(shù)目比GTX 580多,但是芯片面積卻只有后者的一半多一點,這就是從40nm制程工藝進化到28nm的好處。

有一個例外是DRAM 電路,在DRAM存儲單元中,該特征尺寸不是指柵寬,而是指金屬連線所允許的最小間距的一半。概括來說,它描述了該工藝代下加工尺寸的精確度。它并非一定指半導體器件中某一具體結(jié)構(gòu)的特征尺寸,而是一類可以反映出加工精度的尺寸的平均值。它最直觀地反映出:集成電路通過微電子制造工藝加工生產(chǎn)能達到更大的集成密度。

02 工藝節(jié)點進步可帶來功耗進一步減少

工藝節(jié)點的進步也帶來了理論上功耗的降低。因為晶體管縮小可以降低單個晶體管的功耗,因為按照等比例縮小的規(guī)則,柵壓(Vds)會減小,柵壓減小會降低整體芯片的供電電壓,進而降低功耗。

但是從物理原理上說,隨著工藝節(jié)點的進步芯片的單位面積功耗并不跟著降低。因此這成為了晶體管縮小的一個嚴重障礙,因為理論上的計算是理想情況,實際上,芯片的功耗會隨著集成度的提高而提高。在2000年左右的時候,人們已經(jīng)預測,根據(jù)摩爾定律的發(fā)展(晶體管)繼續(xù)縮小下去,假如沒有什么技術(shù)進步的話,10多年后,其功耗密度可以達到火箭發(fā)動機的水平,這樣的芯片是不可能正常工作的。即使達不到這個水平,溫度太高也會影響晶體管的性能。

事實上,業(yè)界現(xiàn)在也沒有找到真正徹底解決晶體管功耗問題的方案,現(xiàn)在的做法是一方面降低電壓(功耗與電壓的平方成正比),一方面不再追求時鐘頻率。因此在2005年以后,CPU頻率不再增長,性能的提升主要依靠多核架構(gòu)。這個被稱作“功耗墻”。“功耗墻”的存在使得晶體管的縮小不能再任意下去。

03 半導體制造對工藝節(jié)點的影響

在微米時代,工藝節(jié)點可以看作是與晶體管的柵寬(溝道長度)劃等號。工藝節(jié)點的數(shù)字越小,溝道長度也越小,晶體管的尺寸也越小。但是在22nm節(jié)點之后,情況有了變化。晶體管的實際尺寸,或者說溝道的實際長度,不一定與這個節(jié)點相等。比方說,英特爾的14nm工藝的晶體管,溝道長度其實是20nm。這是為什么呢?

這要從硅原子談起。硅原子直徑是納米級的,硅原子半徑為110皮米,也就是0.11納米,直徑0.22nm。如果把晶體管的溝道縮小到10nm,就意味著大約是45個硅原子排在一起的長度(不考慮原子間距的情況下),這時在經(jīng)典物理理論下的晶體管的電流模型已不再適用。用經(jīng)典的電流理論計算電子的傳輸,電子在分布確定之后,仍然被當作一個粒子來對待,而不考慮它的量子效應。因為尺寸大不需要。但是越小就不行了,就需要考慮它的各種復雜的物理效應。

其次,一種叫做“短溝道效應”的現(xiàn)象也會對晶體管的性能帶來影響,“短溝道效應”帶來的直接損害是柵極電壓不能有效關閉晶體管,導致漏電流產(chǎn)生,浪費大量功耗。這部分漏電不能小看,“短溝道效應”引起的這部分漏電流導致的能耗,可以占到總能耗的一半。

另一個制造工藝的極限是由制造設備帶來的,具體來說就是光刻機的分辨率制約。光刻機的分辨率與光源有關系,光源的聚焦性能越好,分辨率越高,能夠刻出的線條就越細。在250nm工藝以前的光刻工藝使用的是汞燈光源,為了提高分辨率,從180nm開始采用波長為248nm的KrF激光作為曝光光源,130nm和90nm工藝采用波長為193nm的ArF激光光源,從65nm工藝開始采用波長更短的激光光源。

評論