- 全球知名電子設計創新領先公司Cadence設計系統公司今日宣布,其數字和定制/模擬分析工具已通過臺積電公司16FF+制程的V0.9設計參考手冊(Design Rule Manual,DRM) 與SPICE認證,相比于原16納米FinFET制程,可以使系統和芯片公司通過此新工藝在同等功耗下獲得15%的速度提升、或者在同等速度下省電30%。目前16FF+ V1.0認證正在進行中,計劃于2014年11月實現。Cadence也和臺積電合作實施了16FF+ 制程定制設計參考流程的多處改進。此外,Cadence也

- 關鍵字:

Cadence 臺積電 FinFET

- 全球知名電子設計創新領先公司Cadence設計系統公司,今日宣布臺積電采用了Cadence®16納米FinFET單元庫特性分析解決方案。由Cadence和臺積電共同研發的單元庫分析工具設置已在臺積電網站上線,臺積電客戶可以直接下載。該設置是以Cadence Virtuoso® Liberate® 特性分析解決方案和Spectre® 電路模擬器為基礎,并涵蓋了臺積電標準單元的環境設置和樣品模板。

利用本地的Spectre API整合方案,Liberate和Spect

- 關鍵字:

Cadence 臺積電 FinFET

- 鰭式場效電晶體(FinFET)及三維積體電路(3DIC)引爆半導體業投資熱潮。行動裝置與物聯網(IoT)市場快速成長,不僅加速半導體制程技術創新,晶圓廠、設備廠等業者亦加足馬力轉往3D架構及FinFET制程邁進,掀動半導體產業龐大的設備與材料投資風潮。

應用材料集團副總裁暨臺灣區總裁余定陸表示,3DIC及FinFET制程將持續引爆半導體業的投資熱潮,亦促使創新的設備材料陸續問世。

應用材料(AppliedMaterials)集團副總裁暨臺灣區總裁余定陸表示,隨著行動裝置的功能推陳出新,及聯

- 關鍵字:

FinFET 半導體

- 應用材料公司今天宣布全新推出Applied Varian VIISta® 900 3D系統。作為業內領先的中電流離子注入設備,該系統專為2x納米以下節點的FinFET和3D NAND制程而開發,具有超凡的控制能力,可以幫助高性能、高密度的復雜3D器件實現器件性能優化,降低可變性,提高良率,是應用材料公司在精密材料工程領域的又一重大突破。

VIISta 900 3D系統能有效提高離子束角度精度和束線形狀準確度,并且還能夠出色的控制離子劑量和均勻性,從而幫助客戶實現制程的可重復性,優化器件性

- 關鍵字:

VIISta 900 3D 2x納米 FinFET

- Needham & Co.半導體設備分析師Edwin Mok 27日針對晶圓代工領域提出了透徹分析,認為相關的半導體設備訂單有望在今(2014)年下半年攀高,但16/14奈米FinFET(鰭式場效電晶體)訂單卻將遞延一季。

barron`s.com報導,Mok發表研究報告指出,據了解晶圓代工廠格羅方德(GlobalFoundries;GF)正在提高紐約州Malta廠的20奈米制程產能,而三星電子(Samsung)也正在逐漸增加Austin廠的設備,這似乎支持了近來傳出的高通(Qualco

- 關鍵字:

FinFET 14納米

- 應用材料公司(AppliedMaterials)宣布其全新EnduraVolta化學氣相沈積(CVD)系統加入獨特的鈷金屬后,一舉突破導線技術傳統瓶頸,讓“摩爾定律”持續向下進展到20納米。此外,應材的EnduraVentura實體氣相沈積(PVD)系統不但成功協助客戶降低成本,更可制造出體積更小、耗能更低、性能更高的整合型3D芯片。

在強大技術創新突破的支持下,應用材料公司在營運方面也頗有斬獲。應用材料公司臺灣區總裁余定陸表示,拜半導體事業的蓬勃發展與應用材料公司不

- 關鍵字:

應用材料 FinFET

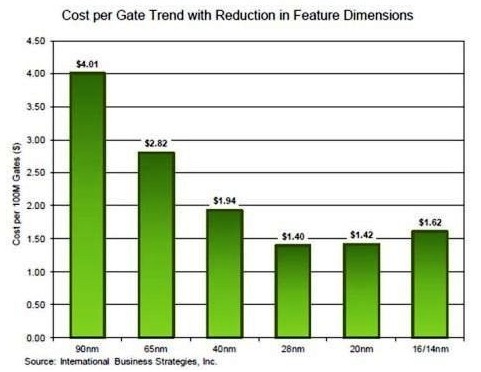

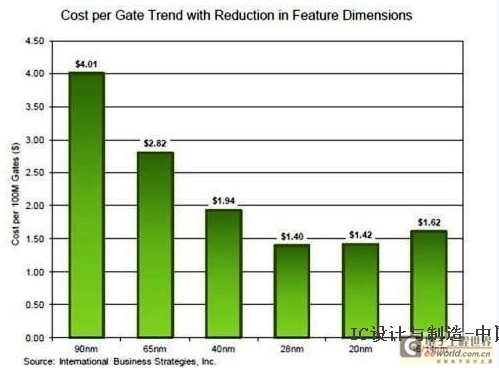

- 在歷史上,半導體產業的成長仰賴制程節點每一次微縮所帶來的電晶體成本下降;但下一代晶片恐怕不會再伴隨著成本下降,這將會是半導體產業近20~30年來面臨的最嚴重挑戰。

具體來說,新一代的20奈米塊狀高介電金屬閘極(bulk high-K metal gate,HKMG) CMOS制程,與16/14奈米 FinFET 將催生更小的電晶體,不過每個邏輯閘的成本也將高出目前的28奈米塊狀HKMG CMOS制程。此成本問題部分源自于在新制程節點,難以維持高參數良率(parametric yields)以及低

- 關鍵字:

FinFET 半導體

- 在歷史上,半導體產業的成長仰賴制程節點每一次微縮所帶來的電晶體成本下降;但下一代晶片恐怕不會再伴隨著成本下降,這將會是半導體產業近20~30年來面臨的最嚴重挑戰。

具體來說,新一代的20奈米塊狀高介電金屬閘極(bulk high-K metal gate,HKMG) CMOS制程,與16/14奈米 FinFET 將催生更小的電晶體,不過每個邏輯閘的成本也將高出目前的28奈米塊狀HKMG CMOS制程。此成本問題部分源自于在新制程節點,難以維持高參數良率(parametric yields)以

- 關鍵字:

FinFET 半導體

- 重點: ·?認證確保精確性方面不受影響,并包含用于65納米至14納米FinFET制程的物理驗證簽收的先進技術 ·?雙方共同的客戶可通過它與Cadence?Virtuoso及Encounter平臺的無縫集成進行版圖設計和驗證版圖 全球電子設計創新領先企業Cadence設計系統公司今天宣布Cadence??Physical?Verification?System?(PVS)通過了GLOBALFOUNDRIES的認證,可用于65納米

- 關鍵字:

Cadence FinFET Virtuoso Encounte

- 大量的金錢和精力都花在探索FinFET工藝,它會持續多久和為什么要替代他們?

在近期內,從先進的芯片工藝路線圖中看已經相當清楚。芯片會基于今天的FinFET工藝技術或者另一種FD SOI工藝的平面技術,有望可縮小到10nm節點。但是到7nm及以下時,目前的CMOS工藝路線圖已經不十分清晰。

半導體業已經探索了一些下一代晶體管技術的候選者。例如在7nm時,采用高遷移率的FinFET,及用III-V族元素作溝道材料來提高電荷的遷移率。然后,到5nm時,可能會有兩種技術,其中一種是環柵F

- 關鍵字:

晶體管 FinFET

- 幾乎所有繼續依靠先進半導體工藝來帶給自己芯片性能與功耗競爭優勢的廠商,紛紛將自己的設計瞄準了即將全面量產的FINFET技術。在這一市場需求推動下,似乎20nm這一代,成為很多代工廠眼中的雞肋,巴不得直接跨越20nm,直奔16/14nm的FINFET。

- 關鍵字:

TSMC FINFET 智能手機 201401

- FinFET給芯片設計業帶來的改變幾乎是革命性的,帶來了各種新的要求,同時也推動了各種創新。

- 關鍵字:

SoC FinFET

- 大家都在談論FinFET——可以說,這是MOSFET自1960年商用化以來晶體管最大的變革。幾乎每個人——除了仍然熱心于全耗盡絕緣體硅薄膜(FDSOI)的人,都認為20nm節點以后,FinFET將成為SoC的未來。但是對于要使用這些SoC的系統開發人員而言,其未來會怎樣呢?

回答這一問題最好的方法應該是說清楚FinFET對于模擬和數字電路設計人員以及SoC設計人員究竟意味著什么。從這些信息中,我們可以推斷出FinFET在系統級意味著什么。

- 關鍵字:

SoC FinFET

- 全球IC矽智財供應商新思科技(Synopsys)力挺臺積電的16納米FinFET(鰭式場效晶體管),全力協助臺積電加入導入這項新制程量產行列。

新思科技是「臺積電大同盟」成員之一,昨天也宣布獲臺積電頒發開放創創新平臺(OIP)「2013年度最佳伙伴獎」,以表彰對臺積電先進制程的貢獻。

臺積電16納米FinFET制程,是對抗英特爾及三星等勁敵的重要技術,臺積電將以大同盟的陣營,聯合IP、自動化工具、設備及芯片設計業的力量應戰。臺積電16納米預定明年第4季試產,2015年第1季量產。

- 關鍵字:

Synopsys FinFET

- 由于ASIC的研發成本居高不下,加上近來FPGA不斷整合更多的功能,同時也突破了過往功耗過高的問題,尤其當進入28奈米制程之后,其性價比開始逼近ASSP與ASIC,促使FPGA開始取代部分ASIC市場,應用范圍也逐步擴張。

附圖: Xilinx揭露未來市場競爭狀況。 資料來源:Xilinx

掌握這樣的趨勢,讓FPGA大廠Xilinx在28奈米的產品營收持續成長。 Xilinx企業策略與行銷資深副總裁Steve Glaser指出,預估今年在28奈米產品線將會有1億美元的營收,市占率高

- 關鍵字:

Xilinx FinFET

3nm finfet介紹

您好,目前還沒有人創建詞條3nm finfet!

歡迎您創建該詞條,闡述對3nm finfet的理解,并與今后在此搜索3nm finfet的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473