TSMC不會在2030年或更晚采用先進的High-NA EUV芯片制造工具 ——英特爾本周剛剛收到了其第一臺:報告

TSMC 不急于采用ASML的High-NA EUV進行大規模生產。

本文引用地址:http://www.104case.com/article/202401/454563.htm

本周,英特爾開始收到其第一臺ASML的0.55數值孔徑(High-NA)極紫外(EUV)光刻工具,它將用于學習如何使用這項技術,然后在未來幾年內將這些機器用于18A后的生產節點。相比之下,據中國Renaissance和SemiAnalysis的分析師表示,TSMC并不急于在不久的將來采用High-NA EUV,該公司可能要在2030年或更晚才會加入這一陣營。

“與英特爾在轉向GAA(計劃在[20A]插入之后)后不久即開始使用High-NA EUV不同,我們預計TSMC將在N1.4時代后(很可能在N1之后,計劃在2030年后啟動)插入High-NA EUV,”中國Renaissance的分析師Szeho Ng寫道。

英特爾的激進工藝技術路線包括從20A(20埃,2納米級別)開始插入RibbonFET門全圍繞(GAA)晶體管和PowerVia背面電源傳遞網絡(BSPDN),然后通過18A對它們進行改進,然后開始使用High-NA EUV工具用于18A后的節點,以提供功耗、性能和面積特性以及最低循環時間。

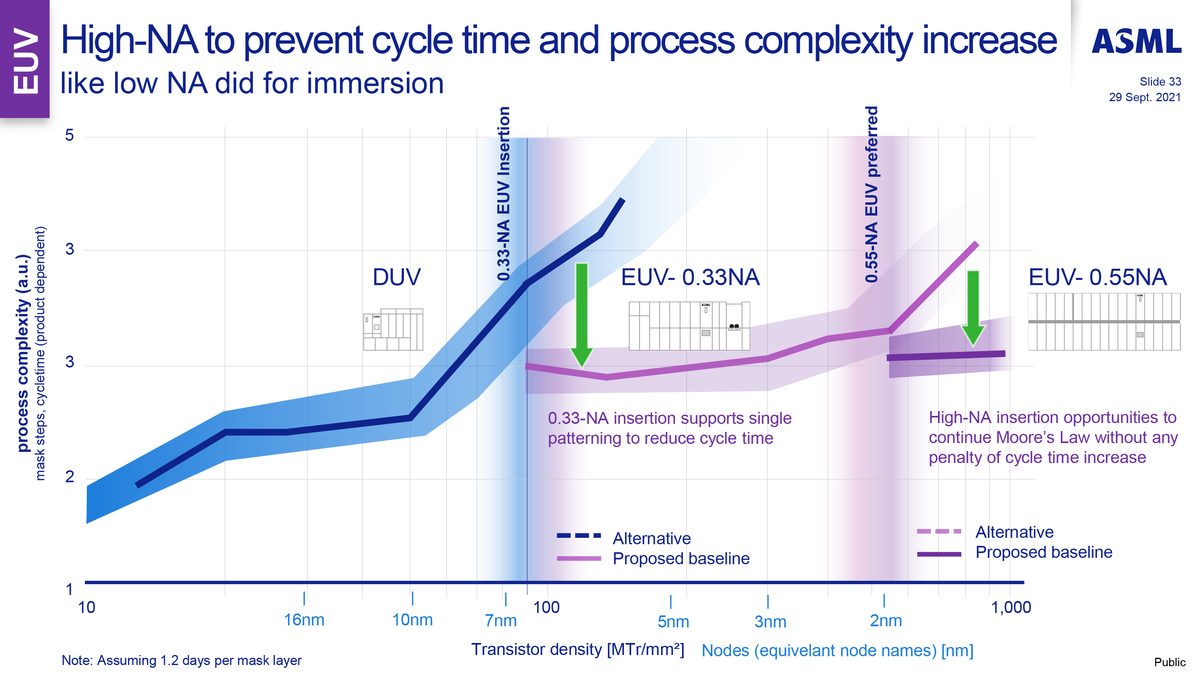

配備0.33數值孔徑透鏡(Low-NA)的現代EUV光刻工具為大規模生產提供了13至16納米范圍內的可實現臨界尺寸,這足以產生26納米的最小金屬間距和使用單一曝光的圖案形成設備產生的估計25至30納米的端到端互連間距。這足以適應3納米級工藝技術(金屬間距在21至24納米之間),但在2納米及以上,金屬間距將縮小到約18至21納米(根據imec的說法),這將需要使用EUV雙圖案形成、圖案形成設備或High-NA單圖案形成。

英特爾計劃從20A開始插入圖案形成(即將進入HVM),然后從18A開始使用High-NA EUV,從而使公司能夠簡化其工藝流程,避免使用EUV雙光刻。然而,High-NA EUV光刻工具的價格顯然比Low-NA EUV掃描儀高得多,但High-NA EUV具有許多特殊性,包括2倍減少的曝光場。

因此,SemiAnalysis和中國Renaissance的分析師認為,使用High-NA EUV機器的成本可能會比最初使用Low-NA EUV雙光刻更高,這就是為什么TSMC可能不愿意立即使用它,以確保低成本,盡管這可能會增加生產復雜性,也許降低晶體管密度。

“盡管Low-NA EUV多光刻在更多曝光通道上的吞吐量較低,但在最初的GAA嘗試中,它可能仍然比High-NA EUV昂貴;High-NA EUV為推動更精細的CD(臨界尺寸)而提供更高的源功率,加速了對投影光學和光掩模的磨損,這超過了更高吞吐量的優勢,”Szeho Ng解釋道。“這與TSMC采用最具成本競爭力的技術來滿足量產市場的做法相一致。”

TSMC在2019年開始使用極紫外(EUV)光刻工具進行芯片的大規模生產,比三星Foundry早數月,比英特爾早數年。英特爾希望在High-NA EUV方面超過三星Foundry和TSMC,這可能會確保一些戰術和戰略上的優勢。唯一的問題是,如果TSMC在2030年或更晚才采用High-NA光刻技術,是否能夠保持其工藝技術的領導地位(即在英特爾之后四到五年)?

評論