臺積電最新進展:2nm正在開發(fā) 3nm和4nm將在明年面世

全球最大的晶圓代工廠,擁有近500個客戶,這就是他們的獨特之處。一方面,公司幾乎可以為提出任何需求的所有客戶提供服務;另一方面,就容量和技術而言,他們必須領先于其他任何人;就產(chǎn)能而言,臺積電(TSMC)是不接受任何挑戰(zhàn),而且未來幾年也不會

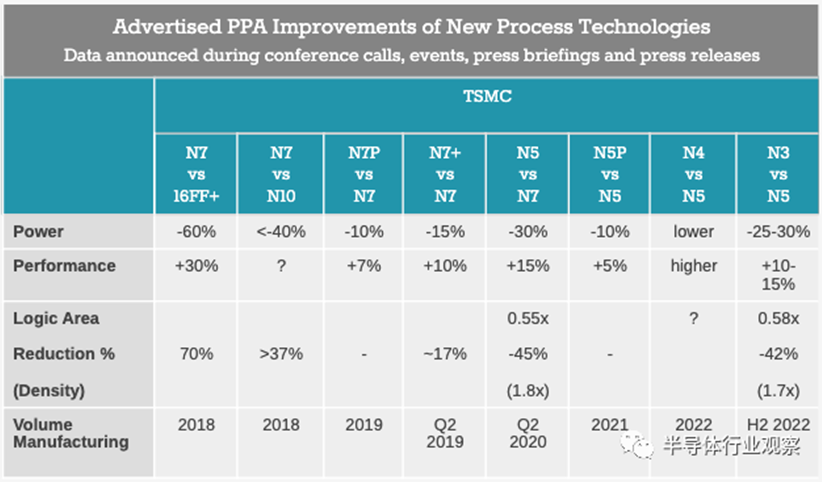

本文引用地址:http://www.104case.com/article/202105/425190.htm臺積電今年300億美元的資本預算中,約有80%將用于擴展先進技術的產(chǎn)能,例如3nm,4nm / 5nm和6nm / 7nm。分析師認為,到今年年底,先進節(jié)點上的大部分資金將用于將臺積電的N5產(chǎn)能擴大,擴大后的產(chǎn)能將提到至每月110,000?120,000個晶圓啟動(WSPM)分析師估計,臺積電的N5晶體管密度約為每平方毫米1.7億個晶體管(MTr / mm 2),如果準確的話,它是當今可用的最密集的技術。相比之下,三星Foundry的5LPE的晶體管密度介乎125 MTR /平方毫米?130 MTR /平方毫米之間,而Intel的10納米設有一個約100 MTR /平方毫米的密度。

魏哲家說:“ N4將利用N5的強大基礎來進一步擴展我們的5 nm系列。” “ N4是具有兼容設計規(guī)則的N5的直接移植,同時為下一波5納米產(chǎn)品提供了進一步的性能,功率和密度增強。N4風險生產(chǎn)的目標是今年下半年,到2022年實現(xiàn)批量生產(chǎn)。

2022年,全球最大的芯片合同制造商將推出其全新的N3制造工藝,該工藝將繼續(xù)使用FinFET晶體管,但預計PPA將大幅提升。

N3將進一步增加EUV層的數(shù)量,但將繼續(xù)使用DUV光刻技術。而且,由于該技術一直在使用FinFET,因此不需要從頭開始重新設計和開發(fā)全新IP的新一代電子設計自動化(EDA)工具,這可能會成為基于Samsung Foundry基于GAAFET / MBCFET的3GAE的競爭優(yōu)勢。。

臺積電首席執(zhí)行官說:“ [N3]風險生產(chǎn)計劃在2021年進行。” “目標是在2022年下半年實現(xiàn)量產(chǎn)。引入N3技術將成為PPA和晶體管技術中最先進的鑄造技術。[…]我們對我們的[N5]和[N3]充滿信心,他們將是臺積電的大型持久節(jié)點。”

Gate-all-around FETs(GAAFET)仍是臺積電發(fā)展路線圖的一部分。預計該公司在其“后N3”技術(可能是N2)中使用新型晶體管。實際上,該公司處于下一代材料和晶體管結構的探路模式,這些材料和晶體管結構將在未來的許多年中使用。

該公司在最近的年度報告中說:“對于先進的CMOS邏輯,臺積電的3nm和2nm CMOS節(jié)點正在順利進行中。” “此外,臺積電加強了探索性的研發(fā)工作,重點放在2nm以外的節(jié)點以及3D晶體管,新存儲器和low-R interconnect等領域,這些領域有望為許多技術平臺奠定堅實的基礎。

至少按臺積電董事長劉德音、德國智庫Stiftung Neue 4月初,臺積電董事長劉德音公開提到,美國和歐洲擴大其半導體晶圓廠產(chǎn)能的計劃是“經(jīng)濟上不現(xiàn)實的”,因為這些計劃是為了滿足其自身需求而進行的,如果整個半導體供應鏈轉(zhuǎn)移到美國和歐洲,或者如果這些地區(qū)計劃擴大產(chǎn)能,則將導致大量“非盈利性”企業(yè)的產(chǎn)生。

評論