8月5日,Cadence公司在上海隆重舉辦年度CDNLive使用者大會。期間,Cadence宣布推出Voltus-Fi定制型電源完整性解決方案,芯片簽收與驗證部門產品營銷總監Jerry Zhao向行業媒體具體講解了新產品的特點。

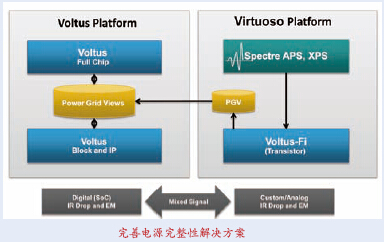

VoltusTM-Fi定制型電源完整性解決方案具備晶體管級的電遷移和電流電阻壓降分析技術(EMIR),獲得晶圓廠在電源簽收中SPICE級精度的認證,從而創建了設計收斂的最快路徑。新的解決方案采用Cadence Spectre? APS(Accelerated P

關鍵字:

Cadence Voltus-Fi SPICE 201409

全球電子設計創新領先公司Cadence設計系統公司 (Cadence Design Systems, Inc) 在上海浦東嘉里大酒店舉辦年度CDNLive使用者大會,會議集聚了Cadence的技術用戶、開發者、業界專家與行業媒體700多人,Cadence工具的開發專家和使用者們面對面分享重要設計與驗證問題的解決經驗,探討高級晶片、SoC和系統的技術潮流趨勢。

5號早上,Cadence公司副總裁兼中國區總經理劉國軍先生首先代表公司歡迎業界客戶、合作伙伴、專家學者及媒體朋友的到來。Cadence總裁

關鍵字:

Cadence CDNLive SoC

全球電子設計創新領先公司Cadence設計系統公司今天宣布推出Cadence® Voltus™-Fi定制型電源完整性解決方案(Cadence® Voltus™-Fi Custom Power Integrity Solution),具備晶體管級的電遷移和電流電阻壓降分析技術(EMIR),獲得晶圓廠在電源簽收中SPICE級精度的認證,從而創建了設計收斂的最快路徑。新的解決方案采用Cadence Spectre® APS(Accelerated Parall

關鍵字:

Cadence Voltus-Fi EMIR

電子產品世界,為電子工程師提供全面的電子產品信息和行業解決方案,是電子工程師的技術中心和交流中心,是電子產品的市場中心,EEPW 20年的品牌歷史,是電子工程師的網絡家園

關鍵字:

零中頻放大器 低噪聲 DIS管腳 Cadence

全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)于2014年5月20日宣布,立即推出基于臺積電16納米FinFET制程的DDR4 PHY IP(知識產權)。16納米技術與Cadence創新的架構相結合,可幫助客戶達到DDR4標準的最高性能,亦即達到3200Mbps的級別,相比之下,目前無論DDR3還是DDR4技術,最高也只能達到2133Mbps的性能。通過該技術,需要高內存帶寬的服務器、網絡交換、存儲器結構和其他片上系統(SoC)現在可以使用Cadence? DD

關鍵字:

Cadence DDR4 PHY IP CRC

全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS)于2014年5月13日宣布,海思半導體(HiSilicon Semi)進一步擴大采用Cadence? Palladium? XP 驗證運算平臺作為其仿真方案,運用于移動和數字媒體System-on-Chip (SoC) 與 ASIC開發。

海思提供通信網絡和數字媒體的ASICs 和 SoCs,包括網絡監控,視頻電話,數字視頻廣播與IPTV解決方案。這些市場的解決方案需要高水準質量與經得起磨練的硬件軟件驗

關鍵字:

Cadence ASICs SoCs

摘要:為了解決高速多層PCB的電源完整性問題,縮短其開發周期,提高其工作性能,以ARM11核心系統為例,提出利用Cadence PI對PCB進行電源完整性分析的方法。通過對電源系統目標阻抗分析,確定去耦電容的數值,數量以及布局;對電源平面進行直流壓降和電流密度分析,改善PCB設計,優化系統的電源完整性。利用動態電子負載搭建的測試平臺,對電源仿真分析后制作的PCB進行測試,系統電源完整性較好,表明分析的結果是有效的。

隨著現代高速信號的速率越來越快,信號邊緣越來越陡,芯片的供電電壓的進一步降低,時鐘頻率和

關鍵字:

Cadence

全球電子設計創新領先企業Cadence設計系統公司日前宣布,展訊通信有限公司(Spreadtrum Inc.)選擇Cadence? Palladium? XP II驗證計算平臺用于系統芯片(SoC)驗證和系統級驗證。展訊使用Palladium XP II的目的是為了縮短芯片的研發周期,并進一步提高其移動芯片開發效率。上述芯片主要用于智能手機、功能手機和消費類電子產品。 “在競爭異常激烈的移動手持設備市場上,功耗低與上市

關鍵字:

Cadence Incisive Palladium

? Xilinx,?Inc.?與?Cadence?設計系統公司日前宣布共同合作開發了業界首個用于在硬件成型之前對基于Xilinx?Zynq?-7000可擴展式處理平臺(EPP)系統進行系統設計、軟件開發與測試的虛擬平臺。該方案進一步改善了Xilinx的基于ARM?處理器平臺的開發環境,為嵌入式軟件設計師改善了開發流程,讓軟件內容能夠驅動硬件設計。 “從2008年開始,Xilinx已經為Zynq-7000?EPP設計了一套全面的開發工

關鍵字:

Xilinx Zynq-7000 Cadence

重點: ·?認證確保精確性方面不受影響,并包含用于65納米至14納米FinFET制程的物理驗證簽收的先進技術 ·?雙方共同的客戶可通過它與Cadence?Virtuoso及Encounter平臺的無縫集成進行版圖設計和驗證版圖 全球電子設計創新領先企業Cadence設計系統公司今天宣布Cadence??Physical?Verification?System?(PVS)通過了GLOBALFOUNDRIES的認證,可用于65納米

關鍵字:

Cadence FinFET Virtuoso Encounte

重點: ·?Cadence?加速并擴展用于ARM??CoreLink??400?interconnect基于IP系統的Interconnect?Workbench解決方案,提高性能驗證和分析速度 ·?Cadence現在提供ARM?Fast模型,可以和Palladium?XP?II平臺結合起來驗證基于ARMv8的嵌入式操作系統 ·?現今可提供支持用于先進聯網、存儲及服務器系統的ARM?AM

關鍵字:

Cadence ARM ARMv8 處理器

全球電子設計創新領先企業Cadence設計系統公司日前宣布其新版Allegro??TimingVision??environment加速高速接口設計高達67%。使用Cadence??Allegro?PCB?Designer中的TimingVision?environment,能大大縮短高速PCB接口設計周期,并確保接口信號滿足時序要求。如今先進的主流協議,包括DDR3/DDR4、?PCI?Express及SATA等協議,隨

關鍵字:

Cadence Allegro PCB SATA Layout

全球電子設計創新領先企業Cadence設計系統公司日前宣布推出Tensilica? Imaging and Video Processor-Enhanced Performance (IVP-EP)處理器,它是IVP產品線中最新一款圖像和視頻數據處理器。IVP-EP是相機圖像處理、視頻后期處理、手勢識別、汽車駕駛輔助及計算機視覺等應用的理想選擇,它基于全新和經過優化的架構,既可以作為獨立的可配置核使用,也是一個完備的預構建子系統,可以很容易地集成到片上系統。

關鍵字:

Cadence Tensilica IVP-EP

全球電子設計創新領先企業Cadence設計系統公司和Sensory日前宣布,他們進一步降低其行業領先的超低功率基于DSP語音激活解決方案的功耗,這是對其它終開啟功能(例如傳感器融合環境感知和臉部激活)的理想補充。 Cadence? Tensilica? HiFi Mini音頻/語音DSP IP采用Sensory TrulyHandsfree? 解決方案,在28納米低功率流程中使用時消耗的功率低于17微瓦,與早期版本相比,功耗降低33%,從而成為理想的offload解決方案,用于應用程序處理器,適合需要始終

關鍵字:

Cadence Sensory Tensilica

cadence介紹

EDA仿真軟件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監控半導 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473