- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)日前宣布,瑞昱半導體公司(Realtek Semiconductor Corp)獲得Cadence Tensilica(Cadence? Tensilica?)授權,可使用HiFi 音頻/語音DSP(數字信號處理器)IP內核,配合Sensory公司(IC和嵌入式軟件解決方案提供商)的TrulyHandsFree?方案一起,用以實現長時開啟(Always-on)語音控制與識別技術。

- 關鍵字:

Cadence 瑞昱 DSP

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)與上海華力微電子有限公司,日前共同宣布華力微電子基于Cadence ? Encounter? 數字技術交付出55納米平臺的參考設計流程。從現在起,華力微電子首次在其已建立的55 納米工藝平臺上實現了從 RTL到GDSII的完整流程,它也是Cadence與上海華力緊密合作的結果。

- 關鍵字:

Cadence 華力 納米

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)日前宣布推出全新用于PCIe 3.0的SpeedBridge? Adapter。它為設計師們提供了一個重要的工具,來驗證和確認他們的PCI Express (PCIe) 設計。

- 關鍵字:

Cadence PCIe SoC

- 益華電腦(Cadence Design Systems)近日宣布兩項成功合作案例,其一為設計服務業者創意電子(GUC)運用Cadence Encounter數位設計實現系統(Digital Implementation System,EDI)與Cadence Litho Physical Analyzer,成功地完成了20nm系統晶片(SoC)測試晶片的試產。此外晶圓代工大廠聯電(UMC)已經采用Cadence 「設計中(in-design)」與signoff DFM (design-for-manufa

- 關鍵字:

Cadence 制程設計

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS)日前宣布,歷經廣泛的基準測試后,半導體制造商聯華電子(NYSE:UMC;TWSE:2303)(UMC)已采用Cadence? “設計內”和“簽收”可制造性設計(DFM)流程對28納米設計進行物理簽收和電學變量優化。

- 關鍵字:

聯華電子 Cadence DFM

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 日前宣布推出用于實現電學感知設計的Virtuoso?版圖套件,它是一種開創性的定制設計方法,能提高設計團隊的設計生產力和定制IC的電路性能。

- 關鍵字:

Cadence Virtuoso EAD

- 為專注于解決先進節點設計的日益復雜性,全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 日前宣布,臺積電已與Cadence在Virtuoso定制和模擬設計平臺擴大合作以設計和驗證其尖端IP。

- 關鍵字:

Cadence Virtuoso 臺積 PDKs

- 全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 日前宣布,設計服務公司創意電子(GUC)使用Cadence? Encounter?數字實現系統(EDI)和Cadence光刻物理分析器成功完成20納米系統級芯片(SoC)測試芯片流片。雙方工程師通過緊密合作,運用Cadence解決方案克服實施和可制造性設計(DFM)驗證挑戰,并最終完成設計。

- 關鍵字:

Cadence DFM

- Cadence Encounter數字實現系統與Cadence光刻物理分析器

可降低風險并縮短設計周期

全球電子設計創新領先企業Cadence設計系統公司(NASDAQ:CDNS) 今天宣布,設計服務公司創意電子(GUC)使用Cadence? Encounter?數字實現系統(EDI)和Cadence光刻物理分析器成功完成20納米系統級芯片(SoC)測試芯片流片。雙方工程師通過緊密合作,運用Cadence解決方案克服實施和可制造性設計(DFM)驗證挑戰,并最終完成設計。

在開發過程中

- 關鍵字:

Cadence 20納米 SoC

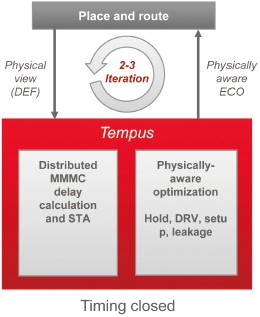

- 為簡化和加速復雜IC的開發,Cadence 設計系統公司不久前推出Tempus時序簽收解決方案。這是一款新的靜態時序分析與收斂工具,旨在幫助系統級芯片 (SoC) 開發者加速時序收斂,將芯片設計快速轉化為可制造的產品。

- 關鍵字:

Cadence Tempus CPU 201307

- Cadence日前宣布,臺積電(TSMC)在20納米制程對全新的Cadence Tempus時序簽收解決方案提供了認證。該認證意味著通過臺積電嚴格的EDA工具驗證過的Cadence Tempus 時序簽收解決方案能夠確保客戶實現先進制程節點的最高精確度標準。

- 關鍵字:

Cadence 臺積電 Tempus

- 在加速復雜IC開發更容易的當下,益華電腦(Cadence Design Systems, Inc.)發表 Tempus 時序 Signoff解決方案(Timing Signoff Solution),這是嶄新的靜態時序分析與收斂工具,精心設計讓系統晶片(System-on-Chip,SoC)開發人員能夠加速時序收斂,讓晶片設計更快速地投入制造流程。Tempus 時序Signoff解決方案意謂全新的時序signoff工具作法,讓客戶能夠縮短時序signoff收斂與分析,實現更快速的試產,同時創造良率更高

- 關鍵字:

Cadence SoC設計

- 為設計收斂和簽收提供前所未有的性能和容量

Tempus?時序簽收解決方案提供的性能比傳統的時序分析解決方案提升了一個數量級。

可擴展性,能夠對具有上億個實例的設計進行全扁平化分析。

集成的簽收精度的時序收斂環境利用創新的考慮物理layout的ECO技術,可以使設計閉合提前數周時間。

為簡化和加速復雜IC的開發,Cadence 設計系統公司推出Tempus? 時序簽收解決方案。這是一款新的靜態時序分析與收斂工具,旨在幫助系統級芯片 (SoC) 開發者加速時序收斂,將芯片設計快速轉

- 關鍵字:

Cadence Tempus 時序簽收

- 【中國,2013年5月14日】全球電子設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),近日推出新版本Incisive Enterprise Simulator,該版本將復雜SoC的低功耗驗證效率提高了30%。13.1版的Cadence Incisive Enterprise Simulator致力于解決低功耗驗證的問題,包括高級建模、調試、功率格式支持,并且為當今最復雜的SoC提供了更快的驗證方式。

Incisive SimVision Debugger的最新

- 關鍵字:

Cadence SoC

cadence reality介紹

您好,目前還沒有人創建詞條cadence reality!

歡迎您創建該詞條,闡述對cadence reality的理解,并與今后在此搜索cadence reality的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473