從5月29日美國政府頒布對華EDA禁令到7月2日宣布解除,33天時間里中美之間的博弈從未停止,但對于EDA公司來說,左右不了的是政治禁令,真正贏得客戶的還是要靠自身產品的實力。作為芯片設計最前沿的工具,EDA廠商需要深刻理解并精準把握未來芯片設計的關鍵。?人工智能正在滲透到整個半導體生態系統中,迫使 AI 芯片、用于創建它們的設計工具以及用于確保它們可靠工作的方法發生根本性的變化。這是一場全球性的競賽,將在未來十年內重新定義幾乎每個領域。在過去幾個月美國四家EDA公司的高管聚焦了三大趨勢,這些趨

關鍵字:

EDA 3D IC 數字孿生

●? ?全新?Innovator3D IC?套件憑借算力、性能、合規性及數據完整性分析能力,幫助加速設計流程●? ?Calibre 3DStress?可在設計流程的各個階段對芯片封裝交互作用進行早期分析與仿真西門子數字化工業軟件日前宣布為其電子設計自動化?(EDA)?產品組合新增兩大解決方案,助力半導體設計團隊攻克?2.5D/3D?集成電路?(IC)?設計與制造的復雜挑戰。西門

關鍵字:

西門子EDA 3D IC

來自日本東京科學研究所 (Science Tokyo) 的一組研究人員構思了一種名為 BBCube 的創新 2.5D/3D 芯片集成方法。傳統的系統級封裝 (SiP) 方法,即使用焊料凸塊將半導體芯片排列在二維平面 (2D) 中,具有與尺寸相關的限制,因此需要開發新型芯片集成技術。對于高性能計算,研究人員通過采用 3D 堆棧計算架構開發了一種新穎的電源技術,該架構由直接放置在動態隨機存取存儲器堆棧上方的處理單元組成,標志著 3D 芯片封裝的重大進步。為了實現 BBCube,研究人員開發了涉及精確和高速粘合

關鍵字:

2.5D/3D 芯片技術 半導體封裝

存儲設備研發公司Neo Semiconductor Inc.(加利福尼亞州圣何塞)推出了其3D-X-DRAM技術的銦-鎵-鋅-氧化物(IGZO)變體。3D-X-DRAM 于 2023 年首次發布。Neo 表示,它已經開發了一個晶體管、一個電容器 (1T1C) 和三個晶體管、零電容器 (3T0C) X-DRAM 單元,這些單元是可堆疊的。該公司表示,TCAD 仿真預測該技術能夠實現 10ns 的讀/寫速度和超過 450 秒的保持時間,芯片容量高達 512Gbit。這些設計的測試芯片預計將于 2026 年推出

關鍵字:

Neo Semiconductor IGZO 3D DRAM

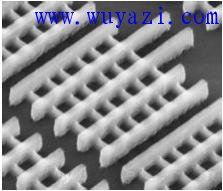

中國的研究人員開發了一種開創性的方法,可以為射頻傳感器構建分辨率低于 10 微米的高縱橫比 3D 微結構。該技術以 1:4 的寬高比實現了深溝槽,同時還實現了對共振特性的精確控制并顯著提高了性能。這種混合技術不僅提高了 RF 超結構的品質因數 (Q 因子) 和頻率可調性,而且還將器件占用空間減少了多達 45%。這為傳感、MEMS 和 RF 超材料領域的下一代應用鋪平了道路。電子束光刻和納米壓印等傳統光刻技術難以滿足對超精細、高縱橫比結構的需求。厚度控制不佳、側壁不均勻和材料限制限制了性能和可擴展性。該技術

關鍵字:

3D 射頻傳感器

英特爾 Arrow Lake 架構的模具照片已經發布,展示了英特爾注入小芯片(tile)的設計的所有榮耀。X 上的 Andreas Schiling 分享了幾張 Arrow Lake 的近距離圖片,揭示了 Arrow Lake 各個圖塊的布局和計算圖塊內內核的布局。第一張照片展示了英特爾臺式機酷睿 Ultra 200S 系列 CPU 的完整芯片,計算圖塊位于左上角,IO 圖塊位于底部,SoC 圖塊和 GPU 圖塊位于右側。左下角和右上角是兩個填充模具,旨在提供結構剛度。計算芯片在 TS

關鍵字:

Arrow Lake Die Shot Intel chiplet

Sandisk Corp. 正在尋求 3D-NAND 閃存的創新,該公司聲稱該創新可以取代基于 DRAM 的 HBM(高帶寬內存)用于 AI 推理應用。當 Sandisk 于 2025 年 2 月從數據存儲公司 Western Digital 分拆出來時,該公司表示,它打算在提供閃存產品的同時追求新興顛覆性內存技術的開發。在 2 月 11 日舉行的 Sandisk 投資者日上,即分拆前不久,即將上任的內存技術高級副總裁 Alper Ilkbahar 介紹了高帶寬閃存以及他稱之為 3D 矩陣內存的東西。在同

關鍵字:

Sandisk 3D-NAND

英特爾最新展示的第二代軟件定義汽車片上系統 (SoC) 器件預示著英特爾在使用小芯片方面邁出了關鍵一步。據分析,這其中部分技術參考借鑒了英特爾收購 Silicon Mobility后在汽車小芯片方面的技術。一年前英特爾承諾為 SDV 提供業界首個基于 UCIe 的開放式小芯片平臺。英特爾將與 imec 合作,確保汽車封裝技術,并致力于成為第一家支持將第三方小芯片集成到其汽車產品中的汽車供應商。該 SoC 在上海 2025 車展上推出,結合了基于不同工藝技術構建的小芯片,為用戶界面提供大型語言模型 AI 支

關鍵字:

英特爾 小芯片 Chiplet

即插即用的Chiplet是人們追求的目標,但UCIe 2.0是否讓我們離這一目標的實現更近了呢?問題在于,當前推動該標準的因素并非是即插即用所要求的那種互操作性。UCIe 2.0于2024年8月發布,它宣稱具有更高的帶寬密度和提升的電源效率,同時還具備支持3D封裝、易于管理的系統架構等新特性。推動這一標準的是行業內的關鍵領導者,包括日月光、阿里巴巴、AMD、Arm、谷歌云、英特爾、Meta、微軟、英偉達、高通、三星電子和臺積電等公司。然而,前沿領域所需的標準可能與市場其他部分的需求不同。YorChip公司

關鍵字:

Chiplet UCIe2.0 封裝 芯片設計

盡管數字技術不斷進步到商業、工業和休閑活動的各個領域,但模擬集成電路 (IC) 在全球半導體市場上仍占有一席之地。今年,收入預計將達到 850 億美元,相當于 10% 的年復合增長率。推動這一需求的是人工智能、物聯網技術和自動駕駛汽車的進步,所有這些都依賴于模擬 IC 來實現傳感和電源管理等功能。與僅處理二進制信號的數字 IC 不同,模擬 IC 可以處理溫度和聲音等連續信號,因此它們對于與物理環境連接至關重要。著眼于這一不斷擴大的市場,兩家總部位于東京的公司 Oki Elec

關鍵字:

薄膜 3D模擬IC 堆疊式IC Chiplet

3D DRAM 將成為未來內存市場的重要競爭者。

關鍵字:

3D DRAM

他表示,開源在新一代信息技術重點應用中持續深化,已從軟件領域拓展至RISC-V為代表的硬件領域。開源RISC-V架構為全球芯片產業發展提供了新的機遇。中國是開源大國,目前已經成為開源RISC-V的重要力量,帶動全球開源事業的發展。倪光南表示,發展RISC-V生態是順時代之勢、應國家之需、答產業之盼,對新時代中國開源體系建設,對推動全球集成電路全產業創新發展都能作出重要貢獻。我國把集成電路產業鏈分為四個環節,即“芯片設計”“芯片制造”“封裝測試”和“下游應用”。為此,發展集成電路產業也應該從全產業鏈的角度考

關鍵字:

risc-v 倪光南 Chiplet

據中國科學院微電子研究所官微消息,針對高密度集成帶來的功耗顯著增加、散熱困難等技術挑戰,微電子所EDA中心多物理場仿真課題組構建了芯粒集成三維網格型瞬態熱流仿真模型,能夠實現Chiplet集成芯片瞬態熱流的高效精確仿真,為芯粒異構集成溫度熱點檢測和溫感布局優化奠定了核心技術基礎。同時,課題組在集成芯片電熱力多物理場仿真方面進行布局,開展了直流壓降、熱應力和晶圓翹曲仿真等研究工作。圖1 各向異性熱仿真圖2 電熱耦合仿真近期,課題組在Chiplet熱仿真工具方面取得新進展。通過對重布線

關鍵字:

中科院 chiplet EDA 物理仿真

日前,紫光國微在投資者互動平臺透露,公司在無錫建設的高可靠性芯片封裝測試項目已于2024年6月產線通線,現正在推動量產產品的上量和更多新產品的導入工作,2.5D/3D等先進封裝將會根據產線運行情況擇機啟動。據了解,無錫紫光集電高可靠性芯片封裝測試項目是紫光集團在芯片制造領域的重點布局項目,也是紫光國微在高可靠芯片領域的重要產業鏈延伸。擬建設小批量、多品種智能信息高質量可靠性標準塑料封裝和陶瓷封裝生產線,對保障高可靠芯片的產業鏈穩定和安全具有重要作用。

關鍵字:

紫光國微 2D/3D 芯片封裝

3d chiplet介紹

您好,目前還沒有人創建詞條3d chiplet!

歡迎您創建該詞條,闡述對3d chiplet的理解,并與今后在此搜索3d chiplet的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473