2.5D/3D 芯片技術(shù)推動(dòng)半導(dǎo)體封裝發(fā)展

來自日本東京科學(xué)研究所 (Science Tokyo) 的一組研究人員構(gòu)思了一種名為 BBCube 的創(chuàng)新 2.5D/3D 芯片集成方法。

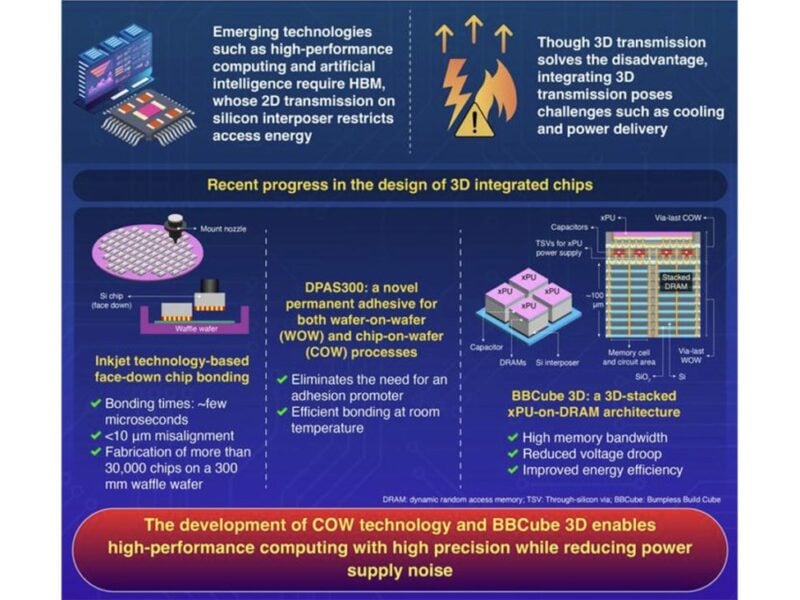

本文引用地址:http://www.104case.com/article/202506/471579.htm傳統(tǒng)的系統(tǒng)級(jí)封裝 (SiP) 方法,即使用焊料凸塊將半導(dǎo)體芯片排列在二維平面 (2D) 中,具有與尺寸相關(guān)的限制,因此需要開發(fā)新型芯片集成技術(shù)。對(duì)于高性能計(jì)算,研究人員通過采用 3D 堆棧計(jì)算架構(gòu)開發(fā)了一種新穎的電源技術(shù),該架構(gòu)由直接放置在動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器堆棧上方的處理單元組成,標(biāo)志著 3D 芯片封裝的重大進(jìn)步。

為了實(shí)現(xiàn) BBCube,研究人員開發(fā)了涉及精確和高速粘合技術(shù)和粘合劑技術(shù)的關(guān)鍵技術(shù)。這些新技術(shù)可以幫助滿足高性能計(jì)算應(yīng)用程序的需求,這些應(yīng)用程序需要高內(nèi)存帶寬和低功耗,同時(shí)降低電源噪聲。

該研究團(tuán)隊(duì)由 Norio Chujo 教授和 Takayuki Ohba 教授以及來自日本東京科學(xué)研究所 (Science Tokyo) 綜合研究所 WOW 聯(lián)盟異構(gòu)和功能集成部門的其他科學(xué)家組成,最初開發(fā)了一種面朝下的晶圓上芯片 (COW) 工藝,以規(guī)避使用焊接互連的限制。利用噴墨技術(shù)和選擇性膠粘劑涂層方法,他們成功地將不同尺寸的芯片順序粘合到 300 mm 的華夫格晶圓上,該晶圓的芯片間距為 10 μm,最小安裝加載時(shí)間不到 10 毫秒。在解釋精確的 COW 工藝時(shí),Chujo 評(píng)論道:“在華夫餅晶圓上制造了 30,000 多個(gè)不同尺寸的芯片,實(shí)現(xiàn)了更高的鍵合速度,而沒有任何芯片脫落故障。

為了實(shí)現(xiàn)這種精確和高速的 COW 工藝,研究人員專注于解決可能影響超薄晶圓多級(jí)堆疊的熱穩(wěn)定性問題。通過精心設(shè)計(jì)化學(xué)特性,他們開發(fā)了一種名為“DPAS300”的新型膠粘劑材料,可用于 COW 和晶圓對(duì)晶圓工藝。這種新型膠粘劑由有機(jī)-無機(jī)雜化結(jié)構(gòu)組成,在實(shí)驗(yàn)研究中表現(xiàn)出明顯的粘附性和耐熱性。

最后,為了實(shí)現(xiàn)高內(nèi)存帶寬并提高 BBCube 的電源完整性,科學(xué)家們采用了 3D xPU-on-DRAM 架構(gòu),并通過新的配電高速公路進(jìn)行了增強(qiáng)。這包括在 xPU 和 DRAM 之間嵌入電容器,在華夫格晶圓上實(shí)施再分布層,以及在晶圓通道和 DRAM 劃線中放置硅通孔。“這些創(chuàng)新將數(shù)據(jù)傳輸所需的能量降低到傳統(tǒng)系統(tǒng)的五分之一到二十分之一,同時(shí)還將電源噪聲抑制到 50 mV 以下,”Chujo 說,并強(qiáng)調(diào)了 3D 堆疊計(jì)算架構(gòu)的優(yōu)勢(shì)。

總而言之,Science Tokyo 的研究人員開發(fā)的 3D 芯片集成技術(shù)有可能改變下一代計(jì)算架構(gòu)。

圖片:BBCube? — 無凹凸塊構(gòu)建立方體。無焊球三維半導(dǎo)體集成技術(shù)可以解決傳統(tǒng) SiP 方法帶來的挑戰(zhàn)。圖片來源:東京科學(xué)研究所。

評(píng)論