HBM、先進封裝利好硅晶圓發展

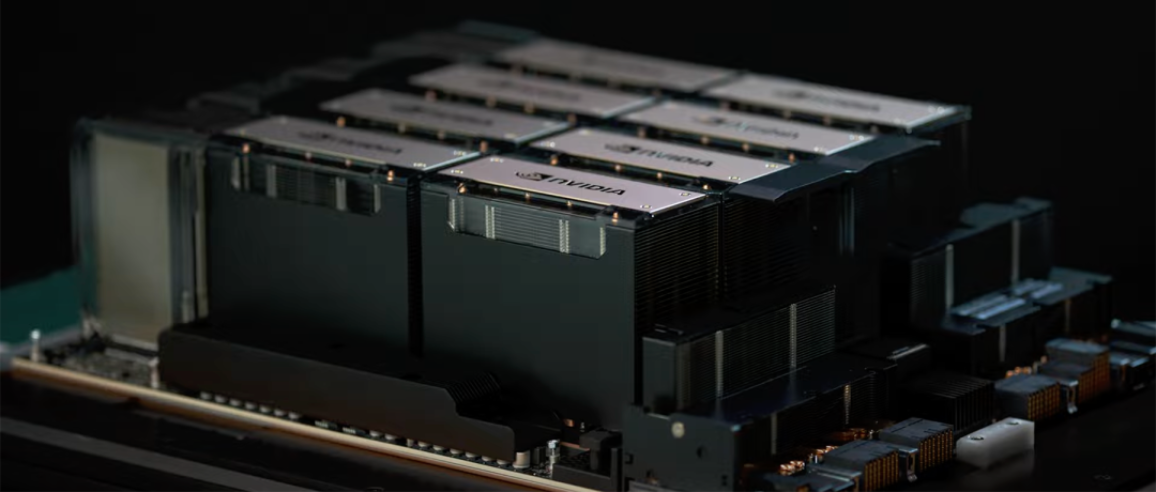

隨著人工智能技術快速發展,AI芯片需求正急劇上升,推動先進封裝以及HBM技術不斷提升,硅晶圓產業有望從中受益。

本文引用地址:http://www.104case.com/article/202407/460608.htm近期,環球晶董事長徐秀蘭對外透露,AI所需的HBM內存芯片,比如HBM3以及未來的HBM4,都需要在裸片(die)上做堆疊,層數從12層到16層增加,同時結構下面還需要有一層基底的晶圓,這增加了硅晶圓的使用量。

此前,媒體報道,AI浪潮之下全球HBM嚴重供不應求,原廠今明兩年HBM產能售罄,正持續增加資本投資,擴產HBM。據業界透露,相較于同容量、同制程的DDR5等內存技術,HBM高帶寬存儲芯片晶圓的尺寸增大了35%~45%;同時,HBM制造工藝的復雜性導致晶圓的良率比DDR5低20%~30%。良率的降低意味著在相同的晶圓面積上,能夠生產出合格芯片的數量減少,以上兩個因素也意味著市場需要耗費更多硅晶圓以滿足HBM的生產。

除了存儲器之外,先進封裝技術創新也對硅晶圓帶來有利影響。徐秀蘭表示,先進封裝所需的拋光片也比之前要多,原因是封裝變立體,結構制程也發生改變,部分封裝需要的晶圓量可能會比過去多一倍。隨著明年先進封裝的產能開出,需要用到的晶圓數量將更加可觀。

CoWoS是當前主流的先進封裝技術,目前供不應求。

全球市場研究機構TrendForce集邦咨詢數據顯示,英偉達B系列包含GB200、B100、B200等將耗費更多CoWoS產能,臺積電(TSMC)亦提升2024全年CoWoS產能需求,預估至年底每月產能將逼近40k,相較2023年總產能提升逾150%;2025年規劃總產能有機會幾近倍增,其中英偉達需求占比將逾半數。

業界指出,過去半導體先進制程發展,die size縮小,減少了晶圓使用量。如今,在AI推動之下,封裝立體化,助力晶圓使用量的提升,進而助力硅晶圓產業發展。但要注意的是,硅晶圓迎來利好的同時,HBM、先進封裝技術的發展對硅晶圓質量、平整度、純度等方面提出了更高的要求,這也將促使硅晶圓廠商做出相應的調整,以應對AI大勢。

評論