chiplet phy designer 文章

最新資訊

半導體周要聞2022.5.23- 2022.5.271. 中國半導體TOP 25榜單去年雖然面臨著疫情、缺芯、漲價等各種不確定性因素,但是2021年半導體行業景氣度高漲,終端智能化需求和供應鏈本土化趨勢越發明顯,中國半導體供應商也迎來了發展良好的一年。Gartner最近發布了中國前25名半導體供應商的排名情況。下圖是Gartner統計的中國前25名半導體供應商排名(僅供參考,如有不同意見,歡迎文末留言)。整體來看,前十名的企業營收都已達10億美元左右,即使是第25名的廠商營收也在5億美元左右,這說明了中國

關鍵字:

半導體 市場 臺積電 chiplet 芯片

隨著信息技術的快速發展,基于嵌入式GUI的人機界面顯示技術日漸成熟從而被應用到更多的行業和領域,其在醫療行業也得到了推廣,并成為了醫療器械數字化、智能化建設的重點。本文研究了一種基于GUIDesigner人機界面系統,通過硬件電路設計及軟件系統進行實現;該系統設計簡便,適用性強,可以廣泛應用于醫療器械行業及其他不同場景。

關鍵字:

人機界面 GUI Designer 系統設計 202204

2022年4月12日,專注先進工藝IP自主研發與服務的中國IP領先企業芯耀輝今日宣布正式加入UCIe(Universal Chiplet Interconnect Express)產業聯盟。作為大陸首批加入該組織的中國IP領先企業,芯耀輝將與UCIe產業聯盟全球范圍內其他成員共同致力于UCIe 1.0版本規范和下一代UCIe技術標準的研究與應用,結合自身完整的先進高速接口IP產品的優勢,為推動中國半導體產業先進工藝、先進技術的發展及應用做出積極貢獻。 今年3月,芯片制造商英特爾、臺積電、三星聯合日月

關鍵字:

芯耀輝 chiplet UCle

半導體周要聞2022.4.6- 2022.4.81. 麥肯錫:到2030年半導體市場可望達到萬億美元規模麥肯錫基于一系列宏觀經濟假設的分析表明,到2030年,該行業的年平均增長率可能為 6%至8%。而同時半導體行業的平均價格也在增長。中芯國際財報顯示2021年晶圓的ASP上漲了13%,假設全行業平均價格每年增長約 2%,并在當前波動后恢復供需平衡,到本十年末將達到1萬億美元的產業。2. 德勤2022年全球半導體行業展望2022 年,全球半導體芯片行業預計將達到約 6000 億美元。根據德勤分析,過去兩年的

關鍵字:

半導體 chiplet

2022年3月,芯片制造商英特爾、臺積電、三星聯合日月光、AMD、ARM、高通、谷歌、微軟、Meta(Facebook)等十家行業巨頭共同推出了全新的通用芯片互聯標準——UCle。幾乎與此同時,中國IP和芯片定制及GPU賦能型領軍企業芯動科技宣布率先推出國產自主研發物理層兼容UCIe標準的IP解決方案-Innolink? Chiplet,這是國內首套跨工藝、跨封裝的Chiplet連接解決方案,且已在先進工藝上量產驗證成功!▲ Innolink? Chiplet架構圖隨著高性能計算、云服務、邊緣端、企業應用

關鍵字:

Chiplet 芯動科技 UCIe Innolink

2022年4月,中國一站式IP和芯片定制及GPU賦能型領軍企業芯動科技宣布,率先推出國產自主研發物理層兼容UCIe標準的IP解決方案——Innolink? Chiplet。

關鍵字:

Chiplet 芯動科技 UCIe Innolink

“拼接”芯片似乎已經成了芯片圈的新“時尚” 蘋果3月的春季新品發布會發布了將兩塊M1 Max芯片“黏合”而成的M1 Ultra,號稱性能超越Intel頂級CPU i9-12900K和GPU性能天花板NVIDIA RTX 3090。 NVIDIA也在3月的GTC上公布用兩塊CPU"黏合”而成的Grace CPU超級芯片,預計性能是尚未發布的第5代頂級CPU的2到3倍。 更早之前,AMD在其EYPC系列CPU中,也用到了"黏合"這一步驟,讓芯片設計成本減少一半。 自家芯片

關鍵字:

芯片 膠水 Chiplet

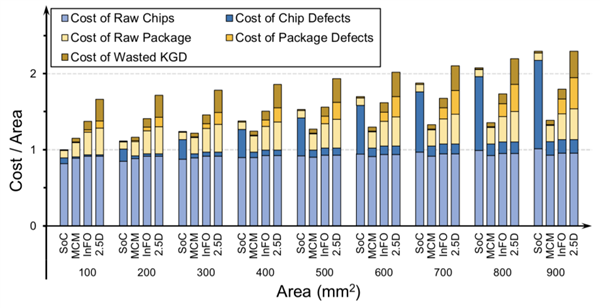

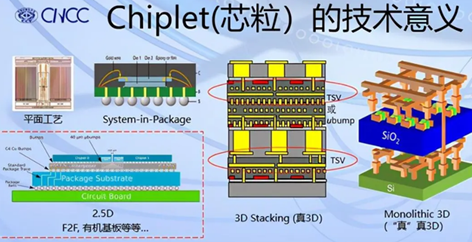

摩爾定律會隨著工藝無限逼近硅片的物理極限而失效,這已經是半導體界老生常談的話題了,但是對于這一問題的解決方案出現了各式各樣的想法。Chiplet,別名小芯片或芯粒,就是其中一種受大廠追捧的解決方法。Chiplet是一種類似打樂高積木的方法,能將采用不同制造商、不同制程工藝的各種功能芯片進行組裝,從而實現更高良率、更低成本。2022年3月,英特爾、AMD、Arm、臺積電、三星、日月光、高通、微軟、谷歌云、Meta十家巨頭聯合,發起了基于Chiplet的新互連標準UCIe。 其實Chiplet的概念早在

關鍵字:

chiplet 芯粒

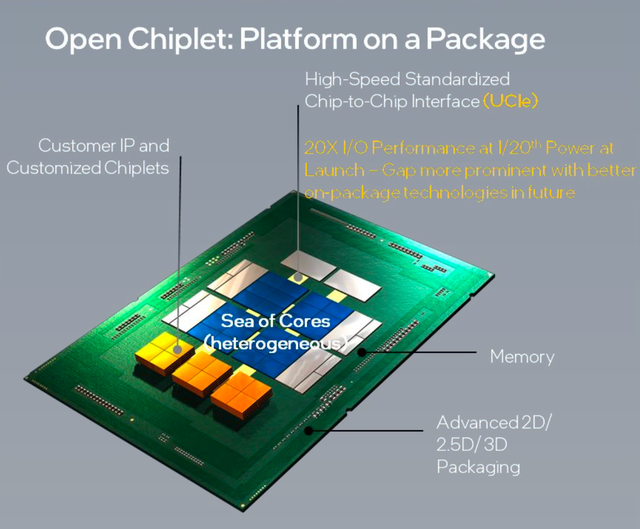

可能很多人已經聽到過Chiplet這個詞,并且也通過各路大咖的報告和演講對Chiplet有了非常多的了解,甚至很多人將其視為延續“摩爾定律”的新希望。日前,Intel聯合AMD、Arm、高通、臺積電、三星、日月光、谷歌云、Meta、微軟等行業巨頭成立Chiplet標準聯盟,制定了通用Chiplet的高速互聯標準“Universal Chiplet Interconnect Express”(以下簡稱“UCIe”),旨在共同打造Chiplet互聯標準、推進開放生態。 其實不管你叫它“芯粒”還是“小

關鍵字:

Chiplet UCIe 小芯片

3月3日,芯原股份在發布的投資者關系活動記錄中稱,公司開始推出一系列面向快速發展市場的平臺化解決方案,其中就包括在2021年上半年芯片流片完成的高端應用處理器平臺。這一高端應用處理器平臺基于高性能總線架構和全新的FLC終極內存/緩存技術,為廣泛的應用處理器SoC產品提供一個全新的實現高性能、高效率和低功耗的計算平臺,并可顯著地降低系統總體成本,旨在面向國內外廣泛的處理器市場,包括PC、自動駕駛、數據中心等領域。目前,芯原股份已與國內外一些客戶進行接觸;另外,芯原股份還將在公司高端應用處理器平臺的基礎上

關鍵字:

芯原股份 chiplet

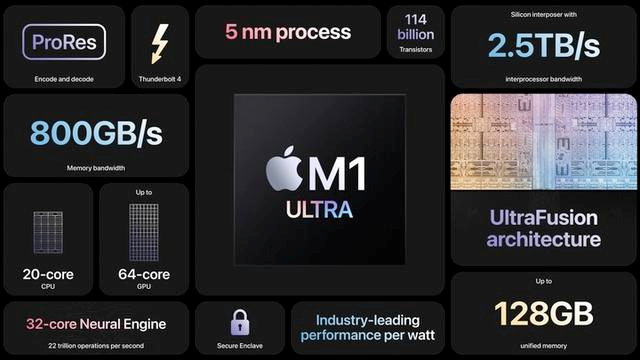

昨日凌晨的蘋果春季發布會上,蘋果發布了最強的 “M1 Ultra”芯片。在大會上,蘋果公布了 M1 Ultra 芯片很多牛逼的參數,比如:晶體管數量1140億顆;20核CPU(16 個高性能內核和 4 個高效內核);最高64核GPU;32核神經網絡引擎;2.5TB/s數據傳輸速率;800GB/s內存帶寬;最高128GB統一內存。M1 Ultra 是 Apple 芯片的又一個游戲規則改變者,它將再次震撼 PC 行業。通過將兩個M1 Max 芯片與我們的 UltraFusion 封裝架構相連接,我們能夠將 A

關鍵字:

蘋果 M1 Ultra chiplet

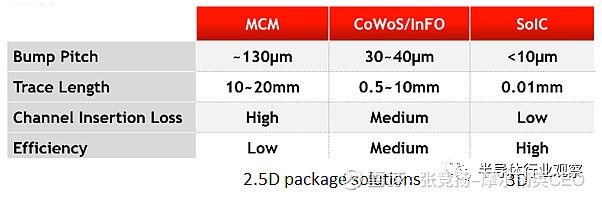

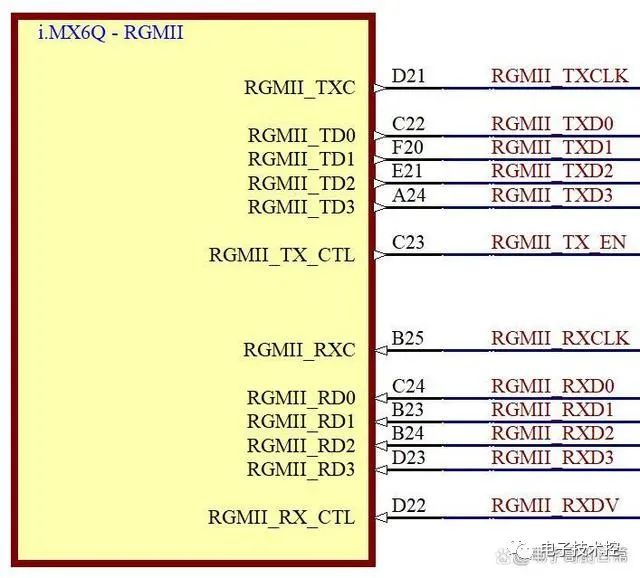

最近日趨熱門的異構和multi-die 2.5D封裝技術推動了一種新型的接口的產生,那就是超短距離(ultra-short reach :USR),其電氣特性與傳統的印刷電路板走線有很大不同。長而有損的連接需要使用SerDes IP的串行通信通道,而短距離接口則支持并行總線體系結構。SerDes信號需要端接(50 ohm),以最大程度地減少反射并減少遠端串擾,從而增加功耗。2.5D封裝內的電氣短路接口無需端接。相比于“recovering”嵌入在串行數據流中的時鐘,并具有相關的時鐘數

關鍵字:

臺積電 chiplet 通信

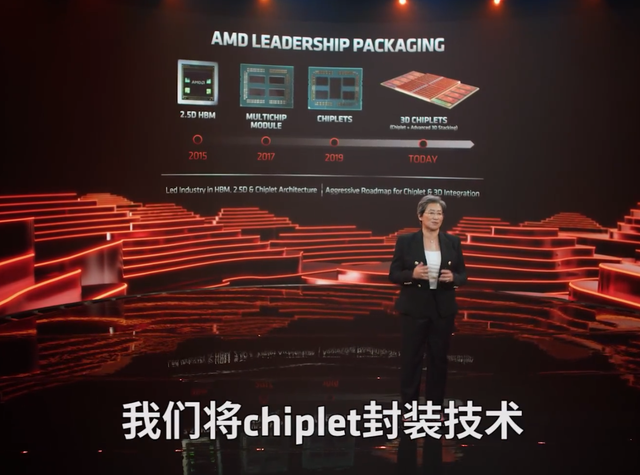

6 月 1 日消息 在今日召開的 2021 臺北國際電腦展(Computex 2021)上,AMD CEO 蘇姿豐發布了 3D Chiplet 架構,這項技術首先將應用于實現“3D 垂直緩存”(3D Vertical Cache),將于今年年底前準備采用該技術生產一些高端產品。蘇姿豐表示,3D Chiplet 是 AMD 與臺積電合作的成果,該架構將 chiplet 封裝技術與芯片堆疊技術相結合,設計出了銳龍 5000 系處理器原型。官方展示了該架構的原理,3D Chiplet 將一個 64MB 的 7n

關鍵字:

AMD chiplet 封裝

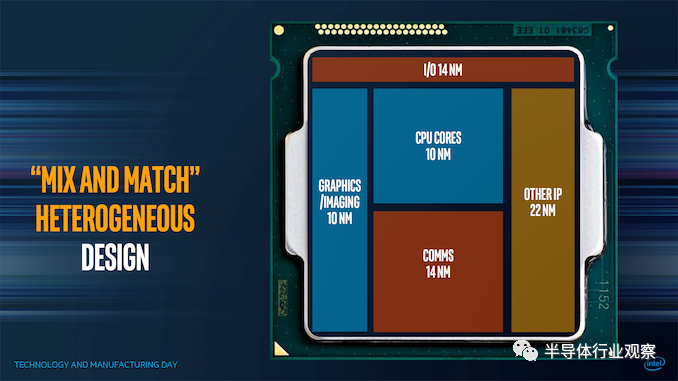

在英特爾2020年架構日活動即將結束的時候,英特爾花了幾分鐘時間討論它認為某些產品的未來。英特爾客戶計算部門副總裁兼首席技術官Brijesh Tripathi提出了對2024年以上未來客戶端產品前景的展望。他表示,他們將以英特爾的7+制造工藝為中心,目標是啟用“Client 2.0”,這是一種通過更優化的芯片開發策略來交付和實現沉浸式體驗的新方法。Chiplet(小芯片)并不是新事物,特別是隨著英特爾競爭對手最近發布的芯片,并且隨著我們進入更復雜的過程節點開發,小芯片時代可以使芯片上市時間更快,給定產品的

關鍵字:

英特爾 chiplet 封裝

Chiplet(小芯片或芯粒)雖然受到工業界和學術界的追捧,之前只是“少數人的游戲”。但隨著UCIe產業聯盟的誕生,一切將成為過往。一個由頂級廠商所主導的Chiplet生態系統已經開始打造,芯片工業發展的新未來開始浮出水面。因何結盟 UCIe(Universal Chiplet Interconnect Express)聯盟包括了英特爾、臺積電、三星、AMD、Arm、高通、日月光、Google Cloud、Meta、微軟等行業巨頭,旨在建立統一的die-to-die(裸片到裸片)互聯標準,打造一個開

關鍵字:

chiplet UCIe 小芯片 芯粒

chiplet phy designer介紹

您好,目前還沒有人創建詞條chiplet phy designer!

歡迎您創建該詞條,闡述對chiplet phy designer的理解,并與今后在此搜索chiplet phy designer的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473