現(xiàn)場可編程門陣列(fpga) 文章

最新資訊

系統(tǒng)的比較,與大家共享:盡管FPGA和CPLD都是可編程ASIC器件,有很多共同特點,但由于CPLD和FPGA結(jié)構(gòu)上的差異,具有各自的特點:①CPLD更適 ...

關(guān)鍵字:

cpld fpga

直方圖對數(shù)字數(shù)據(jù)的分析通常是一種有用的工具。不過,要從一個直方圖獲得可靠的結(jié)果,必須獲得大量數(shù)據(jù),通常是要...

關(guān)鍵字:

FPGA

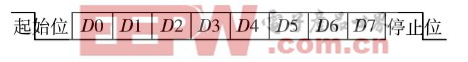

由于FPGA的功能日益強大,開發(fā)周期短、可重復(fù)編程等優(yōu)點也越來越明顯,可以在FPGA芯片上集成UART功能模塊,從...

關(guān)鍵字:

FPGA UART接口

基于FPGA的UART接口模塊設(shè)計,UART(UniversalAnynchronousReceiverTransmitter,通用異步接收發(fā)送器)是廣泛應(yīng)用的串行數(shù)據(jù)傳輸協(xié)議之一,其應(yīng)用范圍遍及計算機外設(shè)、工控自動化等場合。雖然USB傳輸協(xié)議比UART協(xié)議有更高的性能,但電路復(fù)雜開發(fā)難

關(guān)鍵字:

模塊 設(shè)計 接口 UART FPGA 基于

摘要:誤碼測試儀是檢測通信系統(tǒng)可靠性的重要設(shè)備。傳統(tǒng)的誤碼測試儀基于CPLD和CPU協(xié)同工作,不僅結(jié)構(gòu)復(fù)雜,價格昂貴,而且不方便攜帶。基于FPGA的高速誤碼測試儀,采用FPGA來完成控制和測試模塊的一體化設(shè)計,提高了

關(guān)鍵字:

FPGA 誤碼測試 儀的設(shè)計

摘要:目前FIR濾波器的一般設(shè)計方法比較繁瑣,開發(fā)周期長,如果采用設(shè)計好的FIR濾波器的IP核,則開發(fā)效率大為提高。本方案基于Altera公司的CycloneⅡ系列芯片EP2C8Q208C8N,首先利用MATLAB中的濾波器函數(shù)fir2得出需產(chǎn)

關(guān)鍵字:

FPGA FIR 濾波器 性能

摘要:針對信號發(fā)生器時輸出頻率精度高和幅值可調(diào)的要求,采用直接數(shù)字頻率合成(DDS)技術(shù),提出一種基于FPGA的幅值、頻率均可調(diào)的、高分辨率、高穩(wěn)定度的信號發(fā)生器設(shè)計方案。采用AT89S52單片機為控制器,控制FPGA產(chǎn)

關(guān)鍵字:

FPGA 幅值 信號發(fā)生器

摘要:介紹了QDPSK信號的優(yōu)點,并分析了其實現(xiàn)原理,提出一種QDPSK高性能數(shù)字調(diào)制器的FPGA實現(xiàn)方案。采用自頂向下的設(shè)計思想,將系統(tǒng)分成串/并變換器、差分編碼器、邏輯選相電路、四相載波發(fā)生器等4大模塊,用原理圖

關(guān)鍵字:

QDPSK FPGA 調(diào)制器

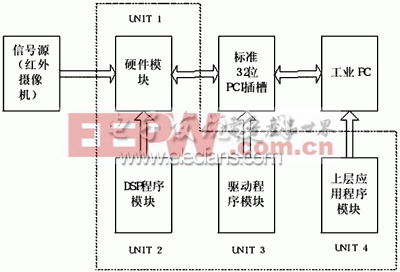

紅外目標識別跟蹤系統(tǒng)的DSP+FPGA實現(xiàn),現(xiàn)場可編程門陣列(FPGA)是在專用ASIC的基礎(chǔ)上發(fā)展出來的,它克服了專用ASIC不夠靈活的缺點。與其他中小規(guī)模集成電路相比,其優(yōu)點主要在于它有很強的靈活性,即其內(nèi)部的具體邏輯功能可以根據(jù)需要配置,對電路的修改和

關(guān)鍵字:

DSP FPGA 實現(xiàn) 系統(tǒng) 跟蹤 目標 識別 紅外

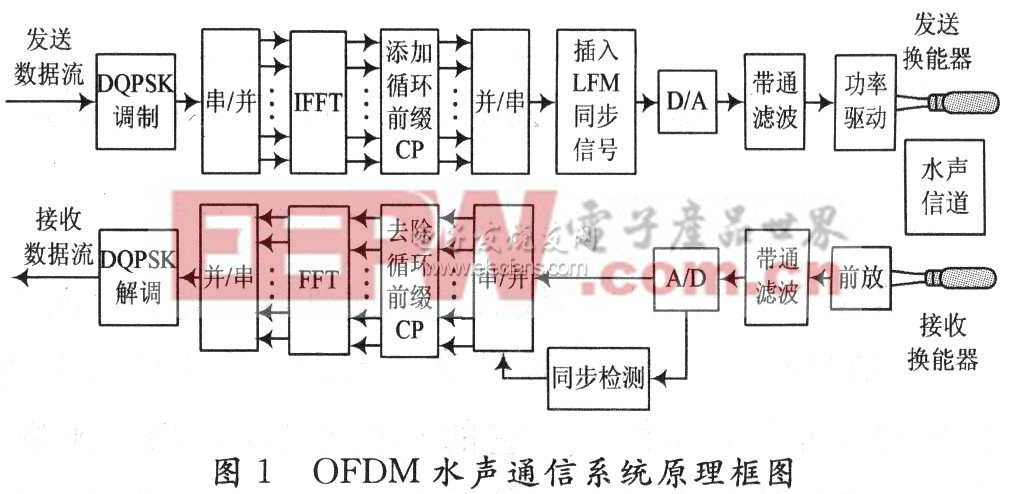

FPGA實現(xiàn)OFDM水聲通信系統(tǒng)定時同步,引 言 正交頻分復(fù)用(Orthogonal Frequency Division Multiplexing,OFDM)技術(shù)是一種多載波調(diào)制技術(shù),它將寬帶信道分解為相互正交的一組窄帶子信道,利用各個子信道進行并行數(shù)據(jù)傳輸,因此其頻譜利用率高、抗多徑衰

關(guān)鍵字:

系統(tǒng) 定時 同步 通信 水聲 實現(xiàn) OFDM FPGA

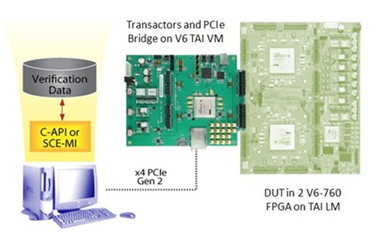

S2C 日前宣布其Verification Module技術(shù)(專利申請中)已可用于其基于Xilinx的FPGA原型驗證系統(tǒng)中。V6 TAI Verification Module可以實現(xiàn)在FPGA原型驗證環(huán)境和用戶驗證環(huán)境之間高速海量數(shù)據(jù)傳輸。用戶可以使用Xilinx ChipScope或者第三方調(diào)試環(huán)境,同時查看4個FPGA。另外,V6 TAI Verification Module還可以用于1.3M~4.7M ASIC門的原型設(shè)計。V6 TAI Verification Module具有PCIe G

關(guān)鍵字:

S2C Xilinx FPGA

引 言數(shù)字相關(guān)器作為軟件無線電的典型應(yīng)用,在擴頻通信中成為必不可少的技術(shù)。在傳統(tǒng)的擴頻通信中,采用模擬器件(如:聲表面波器) 來實現(xiàn)解擴單元,而用數(shù)字相關(guān)器可以增加系統(tǒng)的靈活性和穩(wěn)定性,因此,對數(shù)字相關(guān)器

關(guān)鍵字:

相關(guān) 數(shù)字 實現(xiàn) FPGA DSP

基于FPGA的混合信號驗證流程,隨著SoC設(shè)計上的混合信號組件數(shù)量增加了,基本的功能驗證對于硅初期能否成功也愈來愈重要。FPGA在系統(tǒng)整合難題上加入了一個新特點。在核心上,此新范例-可編程系統(tǒng)單芯片(programmable system chip,PSC)整合FPGA電閘

關(guān)鍵字:

驗證 流程 信號 混合 FPGA 基于

基于FPGA的檢糾錯邏輯算法的實現(xiàn),星載計算機系統(tǒng)中電子器件容易受到空間環(huán)境電磁場的輻射和重粒子的沖擊,從而導(dǎo)致器件運行出錯,特別是存儲器中數(shù)據(jù)容易出現(xiàn)錯誤,需要具有檢糾錯功能的電路模塊對其進行糾正,以免造成嚴重的后果。基于漢明碼的糾錯

關(guān)鍵字:

算法 實現(xiàn) 邏輯 糾錯 FPGA 基于

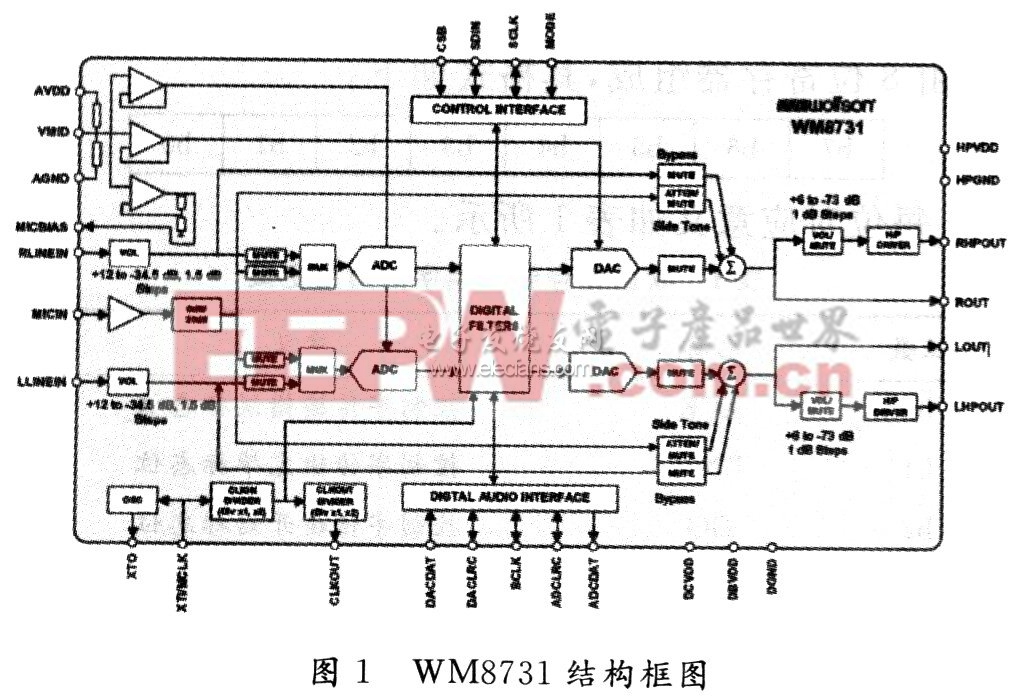

音頻編解碼芯片接口的FPGA應(yīng)用,介紹了音頻編解碼芯片WM8731基于FPGA的接口電路的設(shè)計,包括芯片配置模塊與音頻數(shù)據(jù)接口模塊等,使得控制器只通過寄存器就可以方便地對其進行操作。整個設(shè)計以VHDL和Verilog HDL語言在Max+Plus Ⅱ里實現(xiàn),并進行了驗

關(guān)鍵字:

FPGA 應(yīng)用 接口 芯片 解碼 音頻

現(xiàn)場可編程門陣列(fpga)介紹

您好,目前還沒有人創(chuàng)建詞條現(xiàn)場可編程門陣列(fpga)!

歡迎您創(chuàng)建該詞條,闡述對現(xiàn)場可編程門陣列(fpga)的理解,并與今后在此搜索現(xiàn)場可編程門陣列(fpga)的朋友們分享。

創(chuàng)建詞條

現(xiàn)場可編程門陣列(fpga)相關(guān)帖子

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473