用一個時鐘在FPGA中計算直方圖

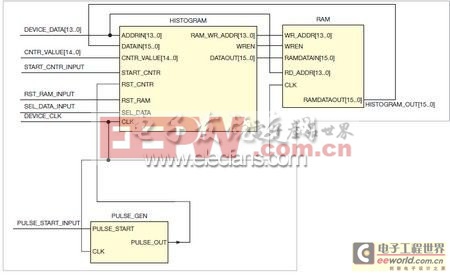

直方圖對數字數據的分析通常是一種有用的工具。不過,要從一個直方圖獲得可靠的結果,必須獲得大量數據,通常是要10萬到100萬個點。如果需要分析一個ADC的數字輸出,可以采用一片FPGA(圖1)。

圖中顯示了直方圖、RAM和脈沖發生器部分,用于捕捉和顯示基于14 位數據計算出來的直方圖。RAM塊是FPGA的內置RAM,而直方圖塊是用于計算的VHDL(高級設計語言)代碼。 來自ADC的14 位并行數據Device_ Data[13..0]進入直方圖塊,并進入RAM的Rd_Addr輸入端。RAM在其地址位置RAMDataOut[ 15..0]上提供數據。這個數據環回到直方圖塊,將其加1后送至一個16 位數據的輸出端DataOut[15..0]。當WREN(寫使能)端為邏輯電平1時,數據被寫在管腳Wr_Addr[13..0]處的地址。這種方法與數據來自Device_Data[13..0]是相同的。

RAM從輸入到輸出有一個固定的延遲。即,當輸入為Rd_Addr時,經過一個固定延遲后,數據出現在其輸出端RAMDataOut。這個延遲隨不同FPGA而改變。要注意這個延遲,使得有兩個時鐘的延遲到Device_Data,然后再計算直方圖。RAM中的延遲應小于兩個時鐘周期;否則,就可能有數據丟失。這個約束限制了Device_Clk的最大頻率。

Cntr_Value給出了用于計算直方圖的輸入數據數量。Pulse_Gen塊產生一個脈沖,進入輸入端Rst_Cntr,用于復位計數器。此時,直方圖部分再次用Cntr_Value的下組輸入數據計算直方圖。Cntr_Value為15 位,但可以增加它,獲得更多的直方圖數據。

Sel_Data與Rst_RAM信號是重置在FPGA RAM中存儲的數據。當Rst_RAM腳出現高信號時,直方圖塊的DataOut腳的所有位均為0。當直方圖塊的Sel_Data輸入腳為高信號時,RAM_Wr_Addr的輸出不是Device_Data,而是一個從0上升至16384的內部生成的斜波。直方圖塊不做計算,因為這樣做會重置RAM的地址。

圖1,直方圖計算電路從一個FPGA的RAM塊中獲取數據。

當FPGA完成了直方圖計算時,RAM就可以選擇Sel_ Data為邏輯高,而將保持Rst_ RAM為邏輯低,從而讀取直方圖數據。RAM地址中的數據順序地退出輸出腳,并且可以將數據傳輸給一臺PC。由于所有塊都以一個單時鐘Device_Clk工作,因此本設計很簡單,有助于滿足時序的約束。可以方便地修改本設計,從而獲得16 位或12 位數據直方圖。

評論