實驗2:1位全加器

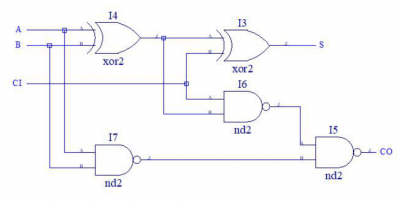

用與非門和異或門設(shè)計一個1位全加器電路,然后在實驗板上實現(xiàn)自己設(shè)計的邏輯電路,并驗證是否正確。

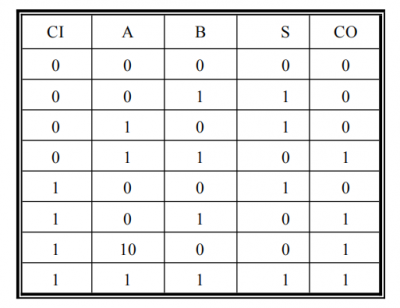

在將兩個多位二進制數(shù)相加時,除了最低位以外,每一位都應(yīng)該考慮來自低位的進位,即將兩個對應(yīng)位的加數(shù)和來自低位的進位三個數(shù)相加。這種運算稱為全加,所用的電路稱為全加器。按照二進制加法運算規(guī)則,可以得到如下表所示全加器真值表。其中,A、B是兩個加數(shù),CI是來自低位的進位,S是相加的和,CO是向高位的進位。將S、CO和A、B、CI的關(guān)系寫成邏輯表達(dá)式則得到:

S=CI’A’B+CI’AB’+CIA’B’+CIAB=A⊕B⊕CI

CO=CI’AB+CIA’B+CI’AB’+CIAB=AB+AC+BC

1位全加器程序清單adder1.v

module adder1 (

input wire a, //輸入的低位進位及兩個加數(shù)cin、a、b

input wire b,

input wire cin,

output wire sum, //輸出的和與進位

output wire cout );

wire s1,s2,s3; //定義中間變量

xor (s1,a,b); //調(diào)用基本異或門

xor (sum,s1,cin);

nand (s2,a,b); //調(diào)用基本與非門

nand (s3,s1,cin);

and (cout,s2,s3);

endmodule

*博客內(nèi)容為網(wǎng)友個人發(fā)布,僅代表博主個人觀點,如有侵權(quán)請聯(lián)系工作人員刪除。