基于FPGA的FIR濾波器的性能研究

摘要:目前FIR濾波器的一般設計方法比較繁瑣,開發周期長,如果采用設計好的FIR濾波器的IP核,則開發效率大為提高。本方案基于Altera公司的CycloneⅡ系列芯片EP2C8Q208C8N,首先利用MATLAB中的濾波器函數fir2得出需產生的FIR濾波器的系數,再導入FIR IP Core,成功完成了FIR數字濾波器的設計。另外分析了階數與不均勻采樣數據對FPGA資源的影響和時生成FIR濾波器的輸出性能的影響,并將實際輸出的幅頻特性圖與我們需要的幅頻特性圖相比較,驗證生成的FIR數字濾波器的性能。

關鍵詞:FIR IP Core;FIR數字濾波器;濾波器系數;幅頻特性圖;EP2C8Q208C8N

在信號處理領域中,常常需要對信號進行加工處理,處理的本質就是信息的變換和提取,是將信息從各種噪聲、干擾的環境中提取出來,變換成我們需要的形式。數字濾波器是由乘法器、加法器和延時單元組成的一種裝置,是一個離散時間系統按預定的算法,將輸入離散時間信號轉換為所要求的輸出離散時間信號的特定功能裝置。在一般情況下,圖像處理及數據傳輸都要求信道具有線性相位特性。有限沖擊響應(FIR)數字濾波器就可以做成具有嚴格的線性相位,同時又可以具有任意的幅度特性。此外,FIR濾波器的單位抽樣響應是有限長的,因而濾波器一定是穩定的。故FIR濾波器廣泛應用于數字系統處理領域。但目前FIR濾波器的設計方法比較繁瑣,開發周期長,本文則介紹了一種簡潔有效的設計方法,并且注重它的資源及性能分析。

隨著IC(Integrated Circuit)技術的發展和EDA(Electronic Design Automatic)工具的完善,各大FPGA器件廠商及第三方都陸續推廣專門的信號處理IP(Intellectual Property)Core,使得基于FPGA的數字信號處理DSP(Digital Signal Processing)系統的開發更加便捷,利用IP Core設計FIR濾波器,設計周期短,占用邏輯資源少,其運算速度相比DSP處理器有很大的提高,故IP核也逐漸成為數字信號處理實現高

速實時的一種方式。

在設計一個FIR濾波器之前,首先要確定濾波器的技術指標。本文是通過MATLAB算出濾波器的系數,導入IP核,就可通過FPGA實現任意的我們需要產生的濾波器。

1 FIR數字濾波器的設計

1.1 FIR數字帶通濾波器的系數設計原理

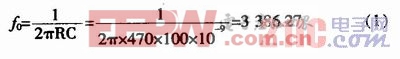

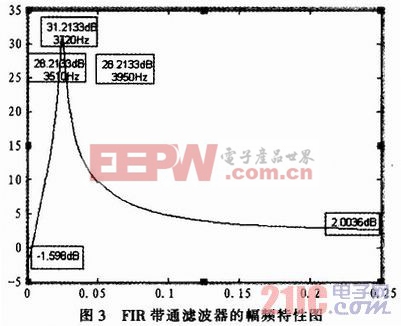

本文以設計帶通濾波器為例介紹如何設計基于IP核的FIR數字濾波器。現有一雙T帶阻濾波電路如圖1所示,測量一系列不同頻率對應的幅值,根據測量的幅頻特性關系,我們可通過MATLAB算出需要設計的帶通濾波器的系數。其帶阻網絡的中心頻率計算公式:

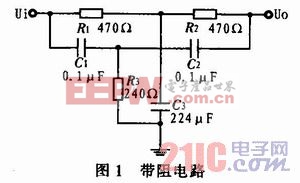

圖2為實際中用毫伏表逐點采樣法測量帶阻網絡的幅頻特性圖,用MATLAB軟件繪制出其幅頻特性圖。由于電阻電容的標稱誤差,實際中測量帶阻電路,其中心頻率點f0在3.7 kHz,衰減31.2133dB。

FIR數字帶通濾波器的系數設計原理是:設帶阻網絡的幅頻特性為H1(jw),FIR帶通網絡的幅頻特性為H2(jw),要實現數字幅頻均衡,則要滿足:

![]()

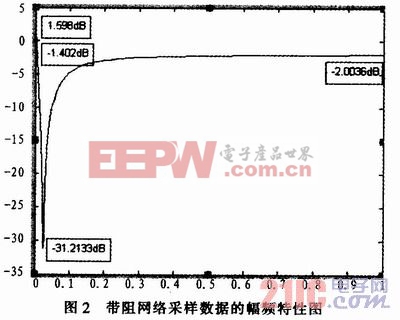

由以上分析知:將帶阻網絡進行頻率采樣,測量帶阻網絡的頻率值和對應的幅度值,則帶通濾波器的幅度值實際可認為是帶阻網絡的幅度值的倒數。由帶阻網絡的幅頻特性,可推算出需要產生的FIR帶通濾波器的性能指標,如圖3所示。

評論