基于FPGA的UART接口模塊設計

UART(UniversalAnynchronousReceiverTransmitter,通用異步接收發送器)是廣泛應用的串行數據傳輸協議之一,其應用范圍遍及計算機外設、工控自動化等場合。雖然USB傳輸協議比UART協議有更高的性能,但電路復雜開發難度大,并且大多數的微處理器只集成了UART,因此UART仍然是目前數字系統之間進行串行通信的主要協議。

本文引用地址:http://www.104case.com/article/150190.htm隨著FPGA的廣泛應用,經常需要FPGA與其他數字系統進行串行通信,專用的UART集成電路如8250,8251等是比較復雜的,因為專用的UART集成電路既要考慮異步的收發功能,又要兼容RS232接口設計,在實際應用中,往往只需要用到UART的基本功能,使用專用芯片會造成資源浪費和成本提高。可以將所需要的UART功能集成到FPGA內部,實現FPGA與其他數字系統的直接通信,從而簡化了整個系統電路,提高了可靠性、穩定性和靈活性。

1 UART簡介

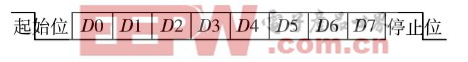

基本的UART通信只需要兩條信號線(RXD,TXD)就可以完成數據的相互通信,接收與發送是全雙工形式,其中TXD是UART發送端,RXD是UART接收端。UART基本特點是:在信號線上有兩種狀態,可分別用邏輯1(高電平)和邏輯0(低電平)來區分。在發送器空閑時,數據線應保持在邏輯高電平狀態。發送器是通過發送起始比特而開始一個字符傳送,起始比特使數據線處于邏輯0狀態,提示接收器數據傳輸即將開始。數據位一般為8位一個字節的數(也有6位7位的情況),低位(LSB)在前,高位(MSB)在后。校驗位一般用來判斷接收的數據位有無錯誤,一般是奇偶校驗。停止位在最后,用以標志UART一個字符傳送的結束,它對應于邏輯1狀態,UART數據幀格式如圖1所示。

圖1 UART數據幀格式

2 UART功能實現

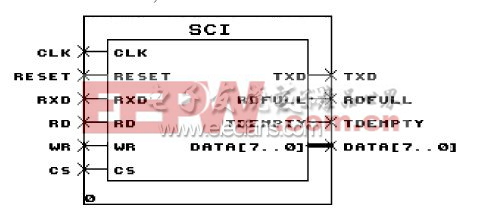

UART可以分解為3個子模塊:波特率發生器模塊;發送模塊;接收模塊。UART的功能主要由VHDL硬件描述語言編程,圖2是編譯后生成的圖元SCI,它包括了UART的最主要的部分,即發送模塊和接收模塊。SCI的外部口線可分為3類:

一是與數字系統的接口,包括數據DATA[7.0],片選CS,讀寫RD、WR,狀態RDFULL、TDEMPTY.這部分接口完成的功能是將待發送的數據寫入SCI或從SCI讀出已接收到的數據。

二是串行通信接口2條線RXD、TXD,其中RXD是接收數據線、TXD是發送數據線,因此,SCI實現的是全雙工通信的設計。

三是系統控制線RESET、CLK,RESET為模塊復位輸入,CLK為模塊時鐘輸入,通信的波特率由CLK來決定(實際的波特率是CLK/4)。

圖2 UART的圖元模塊結構

RDFULL、TDEMPTY為兩個狀態標志位,RDFULL為輸入寄存器滿標志,高電平表示已經接收到一個有效數據并存儲到輸入數據寄存器中,當CS、RD有效將數據讀出后變為低電平無效。

TDEMPTY為輸出寄存器空標志,高電平表示由CS、WR有效寫入到輸出寄存器的數據已經發送完畢,可以向輸出寄存器寫入另外待發送的數據,低電平時表示數據目前正在發送中。

評論