一種基于FPGA的高速誤碼測試儀的設計

摘要:誤碼測試儀是檢測通信系統可靠性的重要設備。傳統的誤碼測試儀基于CPLD和CPU協同工作,不僅結構復雜,價格昂貴,而且不方便攜帶。基于FPGA的高速誤碼測試儀,采用FPGA來完成控制和測試模塊的一體化設計,提高了系統功能擴展性和系統的集成度,使得各個功能模塊在不改動硬件電路的情況下可以相應變化。在發送端發送m序列作為測試數據,其測試速率最高可達到155 Mh/s。由于將物理層上的各協議層的功能集中到FPGA內部實現,減少了硬件和軟件的設計復雜度,并且縮短了系統的開發的周期,具有可升級的特點。

關鍵詞:高速誤碼測試儀;現場可編程門陣列;Vetilog硬件描述語言;模塊圖元;仿真;M序列碼

誤碼分析儀作為數字通信系統驗收、維護和故障查詢的理想工具,廣泛應用于同軸電纜、光纖、衛星及局間中繼等符合CEPT(European Confence of Postal and Telecommunications Administrations)數字系列通信系統傳輸質量的監測。評價一個通信系統的可靠性的指標就是檢測該通信系統在數據傳輸過程中誤碼率的大小,本文設計的高速信號誤碼測試儀,用于對EPON中接收和發送突發光信號的接收模塊的可靠性進行檢測。目前誤碼分析儀的工作模式已發展到如下4種:分析儀模式、發生器模式、分析儀/發生器模式、直通模式。本設計中的誤碼測試儀屬于第3種類型,即該誤碼測試儀可以產生測試的碼流,又可以進行誤碼測試。

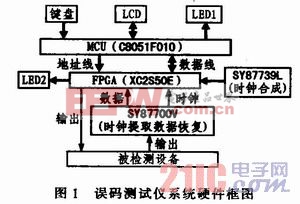

誤碼測試儀主要由發送模塊,接收模塊,顯示模塊,控制模塊等幾個模塊組成,系統硬件結構框圖如圖1所示。其中發送、接收模塊在FPGA中實現,控制模塊由單片機實現,顯示模塊由單片機驅動,這樣使得設計的誤碼分析儀具有體積輕巧,接口豐富,簡單易用,成本低廉,內核可升級等特點。

1 基于FPGA的誤碼測試儀的設計

FPGA在該設計中實現了誤碼測試儀的核心功能,FPGA設計使用的是自頂向下模塊化的設計方法。基于FPGA設計的模塊包括:SY87739L頻率計的控制模塊、SY87700時鐘提取控制模塊、計數模塊、偽隨機序列發送模塊、數據接收模塊、與單片機的通信模塊。

1.1 頻率合成芯片SY87739L的控制模塊

在設計中SY87739L合成的頻率用于偽隨機序列合成的同步時鐘,因為該誤碼測試儀可以測試的頻率有32 Mb/s、64 Mb/s、122 Mb/ s、155 Mb/s 4種。所以該芯片要根據設置的參數合成相應的頻率。具體合成哪一個,由FPGA來實現對SY87739L的控制。

SY87739L(規程式透明3.3 V 10~729 MHz分數N合成器)是一個頻率合成芯片。依照一參考頻率源,它可以合成10~729 MHz范圍內的差分頻率。此外它可以精確地為標準的傳輸協議合成相應的參考頻率。SY87739L合成的頻率是由一個32位的串行輸入的編程數據決定。PROGCS為高電平時,編程數據才會被SY87739L接收。若用戶需要改變編程數據獲得一個新的頻率時,應先將PROGCS設置為高電平,延時一段時間(待32 bit編程數據被SY87739L接收)后在回落到低電平。既在PROGCS的下降沿時,SY87739L會由前一時段接收到32 bit編程數據決定合成新的頻率。具體步驟如下:1)確定編程數據的值;2)設置PROGCS為高電平;3)串行輸入32 bit編程數據(由PROGDI管腳輸入),同時在PROGSK端輸入時鐘信號;4)設置PROGCS為低電平;5)等待LOCKED跳為高電平。

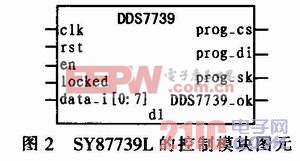

根據SY87739L的工作原理,可以用硬件語言編寫出SY87739L的控制代碼,圖2是由Verilog代碼用Synplify Pro8.1綜合出的圖元。

該模塊控制SY87739L合成32 M頻率功能仿真結果(由ModelSim SE6.1仿真)如圖3所示。

測試文件中給DATA-I賦值為00000001,可以觀察出prog_di串行輸出的編程數據為0000_01100_01101_0100_000_10001_101_101;prog_cs在prog_di有效編程數據輸出為高電平,待編程數據輸出結束后回落到低電平:PROGSK輸出SY87739L的編程時鐘。經分析可以看出SY87739L控制模塊可以實現預想的功能。

1.2 時鐘提取芯片SY87700V的控制模塊

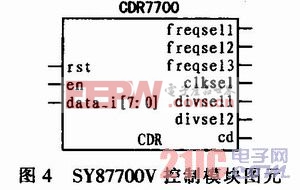

SY87700V對FPGA接收的數據進行時鐘提取和數據恢復。將恢復的數據與接收端產生的本地偽隨機序列進行對比,實現誤碼檢測,兩數據流對比時以提取的時鐘為同步時鐘。SY87700V在提取數據前要預知提取的頻率的范圍,此頻率范圍由FPGA發送給SY87700V。SY87700V的參考時鐘是否進行分頻,也要根據設置的參數由FPGA控制。此外該模塊還要實現FPGA讀取SY87700V的功能,以確定SY87700V是否完成時鐘提取及數據恢復。根據SY87700V的工作原理,可以用硬件語言Verilog編寫程序在FPGA實現控制SY87700V的模塊,圖4是由代碼綜合出的圖元。

評論