S2C為Xilinx原型驗證系統提供突破性驗證模塊技術

—— 實現基于FPGA的原型和用戶驗證環境之間高速數據傳輸并實現對多個FPGA的同時調試

S2C的董事長及首席技術官Mon-Ren Chene先生說:“我們在今年6月份首次發布的Verification module技術是為使用Xilinx原型驗證系統的客戶提供的技術。這是一種可以將用戶的FPGA原型環境和用戶驗證環境接口的突破性技術。由于設計通 常被分割到多個FPGA中,用戶可以有這項新能力同時對多個FPGA進行調試對他們來說非常重要。FPGA原型驗證系統以系統速度或者接近系統速度運行。 通過高速接口,FPGA原型驗證環境可以更容易地連接到實際目標系統環境。”

三種運行模式

通用的S2C V6 TAI Verification Module提供了三種使用模式:驗證模式、調試模式和邏輯模式。 驗證模式使用SCE-MI或定制的C-API通過一條 x4-lane PCIe Gen2通道實現海量數據和PC之間的傳輸。在調試模式中,V6 TAI Verification Module通過使用Xilinx ChipScope或者其它第三方工具從而實現了多個FPGA的同步調試且同時保持用戶的RTL名。在邏輯模式中,用戶可以原型化一個設計,其容量能達到 4.7M門。 所有對Verification Module的調試和驗證設置都是在S2C 的TAI Player Pro™中完成。

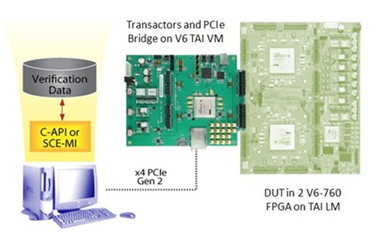

驗證模式

驗證模式利用TAI Verification Module的高速PCIe Gen2接口將大量仿真數據在PC和TAI Logic Module之間進行雙向快速地傳輸。該模式能將原型系統和仿真器直接連接進行同步仿真。用戶可以利用下圖所示的S2C提供的定制C-API或者符合行業 標準的SCE-MI接口:

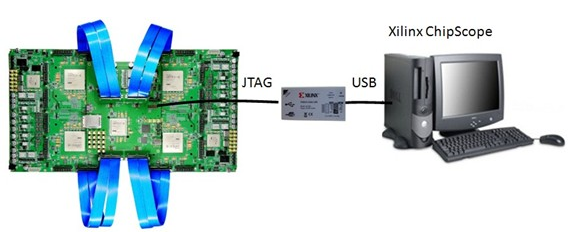

調試模式

調試模式則利用了用戶現有的Xilinx ChipScope或者其它第三方調試環境。V6 TAI Verification Module從Logic Module中的多個FPGA獲取用戶定義的信號并接收到V6 TAI Verification Module,通過JTAG接口與ChipScope連接。

V6 TAI Verification Module 使用Xilinx Chip Scope Analyzer可同時對放在兩塊Dual V6 TAI Logic Module上的FPGA設計進行調試。

最高能見度

每個Virtex 6 FPGA的120信號都接到了V6 TAI Verification Module的FPGA中。用戶能在4 個V6 FPGA中進行120 x N信號的路徑選擇。最初的發布中,N固定在4上,但今后將由用戶定義。用戶所需要做的是在設計綜合前在RTL級選擇Probes并且將它們按照每個 FPGA120個probe來進行分組。S2C的TAI Player Pro自動采用多路復用技術將來自多個FPGA的調試信號發送至V6 TAI Verification Module的單個Xilinx ChipScope,并保留RTL名。將使用Xilinx ChipScope調試過程中的調試數據存儲在V6 TAI Verification Module的存儲器中直到滿足預先設置的觸發條件為止,再將這些調試數據讀取出來。

邏輯模塊

V6 TAI Verification Module可以作為單個原型板,為高達4.7M門容量的小規模SoC或ASIC設計使用。V6 TAI Verification Module可以配備Xilinx LX130T、LX365T 或者SX475T FPGA上,而且在4個LM連接器上共有480個外部I/O,x4 PCIe Gen2接口,4路通過SMA連接器的千兆串行收發器、一個SATA2接口以及一個USB3.0 PHY接口。

配置詳情顯示在下表:

可用性

V6 TAI Verification Module硬件現已供使用。

評論