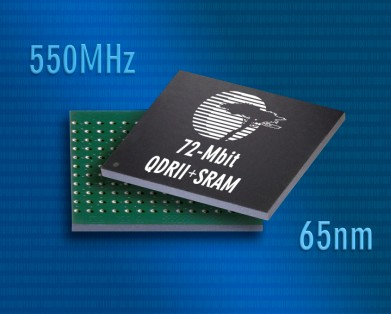

賽普拉斯推出采用 65 納米工藝技術的 SRAM

賽普拉斯-SRAM 領域的業界領先公司,日前宣布,該公司在業界率先推出采用 65 納米線寬的 Quad Data Rate™ (QDR™) 和 Double Data Rate (DDR) SRAM 器件樣品。新推出的 72-Mbit QDRII、QDRII+、DDRII 和 DDRII+ 存儲器采用了賽普拉斯合作伙伴制造商 UMC 開發的工藝技術。新型 SRAM 實現了目前市場上最快的 550 MHz時鐘速度,在 36 位 I/O 寬度的 QDRII+ 器件中可實現高達 80 Gbps 的總數據傳輸速度,而功耗僅為 90 納米 SRAM 的一半。這種新型存儲器非常適用于因特網核心與邊緣路由器、固定與模塊化以太網交換機、3G 基站和安全路由器等網絡應用,而且還能提高醫療影像和軍用信號處理系統的性能。上述產品可與 90 納米 SRAM 引腳兼容,從而幫助網絡客戶提高性能、增加端口密度,而且還不必改變原有的板卡布局。

本文引用地址:http://www.104case.com/article/93939.htm

相對于 90 納米的上一代產品,65 納米的 QDR 和 DDR SRAM 能將輸入輸出電容降低 60%。QDRII+ 和 DDRII+ 器件具有片內終結電阻器 (ODT),消除了外部端需接電阻的要求,因而可提高信號的完整性,降低系統成本,節約板上空間。65 納米產品采用的是鎖相環路 (PLL) 而非延遲鎖相環 (DLL) 技術,其可使數據有效窗口擴展 35%,以幫助客戶縮短開發時間、節約開發成本。

賽普拉斯存儲器和影像部門的執行副總裁 Dana Nazarian 指出:“我們不斷豐富自身的同步 SRAM 產品系列,以期拓展目標市場,擴大市場份額。賽普拉斯致力于推動 SRAM 市場的長期發展,并不斷鞏固我們的領先地位。”

評論