基于SystemC的系統級芯片設計方法研究

為了支持寄存器傳輸級的并行描述,SystemC還采用了與傳統硬件描述語言基本相同的調度模型基于Δ(delta)延遲。一個Δ周期包括求值和更新2個階段,在一個時間點上,這樣的Δ周期會出現直到再求值前后的結果不再發生變化。而在宏觀上,時間并沒有前進。SystemC 2.01調度模型中,在初始化階段(相當于時間0點),所有進程包括方法進程和線程都將執行一次。不同的是,在SystemC中,所有的信號和變量的初始化工作在構造函數中進行,他比其他函數先執行,避免了像Verilog HDL中由于初始化順序不同引起的不同仿真器仿真結果的不一致。

本文引用地址:http://www.104case.com/article/83115.htm為了支持進程同步和通信細化,SystemC支持用戶自定義的接口,端口和通道。接口是方法的集合,但不具體實現這些方法,在C++語法中,他們都是純虛函數。通道具體實現一個或者多個接口。端口定義了他能夠連接的具體的接口類型,只能被用于連接實現了該類型接口的通道。在有些情況下,進程可以直接讀寫通道而不必通過端口,而其他情況下則必須通過端口進程才能讀寫通道。

在SystemC中,進程只調用通道提供的接口方法。雖然接口方法是在通道中實現的,然而他是在進程上下文中被執行的。這被稱作接口方法調用(InteRFaceMethodCall,IMC),接口方法調用和支持不同抽象級別的混合建模是通信細化的基礎。

4 基于SystemC的設計思想和設計流程

用SystemC可以在抽象層次的不同級描述系統。在系統最高層的系統級可以用C/C++描述系統的功能和算法。在系統的硬件實現部分可以在行為級到RTL級用SystemC 的類來描述,系統的軟件部分自然可以用C/C++語言描述。而且,系統的不同部分可以在不同的抽象層次描述,這些描述在系統仿真時可以協同工作。并且,用SystemC不但可以描述要開發的系統本身,還可以描述系統的測試平臺Testbench,以提供測試信號用于系統的仿真。

SystemC由一組描述類的頭文件和一個包含仿真核的連接庫Link Library所組成,在用戶的建模描述程序中必須包括相應的頭文件,然后可以用通常的C++編譯器編譯該程序。在連接Link時要調用SystemC的連接庫產生可執行的系統仿真程序。利用SystemC建模的思想如圖2所示。

基于SystemC的設計流程與以前的設計流程的本質區別在于,使用一種語言就可以完成從系統到RTL、從軟件到硬件的全部設計,整個設計的軟硬件可以協同設計和仿真,恰好彌補了傳統設計方法中的這些不足。

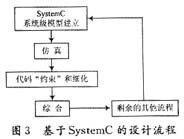

基于SystemC的設計流程如圖3所示。

5 應用實例

下面給出一個基于SystemC設計的實例:RS(15,9)的設計詳細地說明整個設計流程。

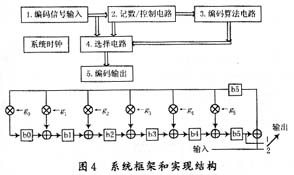

RS(Reed-Solomon)[4]糾錯碼是目前最有效、應用最廣泛的差錯控制編碼之一,是一類具有很強糾錯能力的多進制的線性分組碼,RS(15,9)碼編碼器,主要應用于移動通信系統的差錯控制,由于該編碼器小巧、靈活,糾錯性能好,對于移動通信系統可靠性的提高、復雜度的降低有至關重要的作用[5]。整個系統如圖4所示。

整個設計從用SystemC為整個系統建模開始,同時為模塊建立Testbench。然后使用VC ++6.0和Modelsim進行功能仿真,接著在SystemC可綜合子集的范圍內對代碼進行約束,使用支持SystemC的綜合工具SCC(SystemC Compiler)完成綜合,SystemC的綜合實際上還是靠綜合HDL語言文件得到的網表,而SCC這個工具是SystemC和HDL之間的一個橋梁,因此對于SystemC的綜合首先是將SystemC描述的RTL級電路通過SCC綜合,綜合的結果是生成相應的Verilog文件,在這個轉變過程中,模塊的整體結構被保存,如每一個sc _module被轉換成獨立的Verilog模塊,并存放在module_namev文件中;每一個進程(SC_METHOD)被轉換成帶進程名的always塊;變量和端口也以同樣的名字在Verilog文件中生成。因此,后續流程就與傳統設計語言設計的FPGA流程連接上了。

本文選用Xilinx的SPARTAN2系列的FPGA XC2S50PQ28對本設計進行驗證。軟件平臺主要使用的是Xilinx的集成開發環境ISE。其中第三方工具使用了綜合工具FPGA CompilerⅡ,布局布線工具選用的是ISE中的Webpack suite。

pic相關文章:pic是什么

c語言相關文章:c語言教程

c++相關文章:c++教程

評論