基于SystemC的系統級芯片設計方法研究

隨著集成電路制造技術的迅速發展,SOC設計已經成為當今集成電路設計的發展方向。SO C設計的復雜性對集成電路設計的各個層次,特別是對系統級芯片設計層次,帶來了新挑戰,原有的HDL難以滿足新的設計要求。

本文引用地址:http://www.104case.com/article/83115.htm硬件設計領域有2種主要的設計語言:VHDL和Verilog HDL。而兩種語言的標準不統一,導致軟硬件設計工程師之間工作交流出現障礙,工作效率較低。因此,集成電路設計界一直在尋找一種能同時實現較高層次的軟件和硬件描述的系統級設計語言。Synopsys公司與Coware公司針對各方對系統級設計語言的需求,合作開發了SystemC,他可以較好地實現軟硬件的協同設計,是系統級芯片設計語言的發展趨勢[1]。

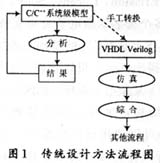

1 傳統的系統級設計方法[1]

在傳統設計方法中,設計的系統級往往使用UML,SDL,C,C++等進行描述以實現各功能模塊的算法,而在寄存器傳輸級使用硬件描述語言進行描述。最廣泛使用的2種硬件描述語言是VHDL和Verilog HDL,傳統的系統設計方法流程如圖1所示。從圖中不難看出,傳統的設計方法會出現如下弊端:

首先,設計人員需要使用C/C++語言來建立系統級模型,并驗證模型的正確性,在設計細化階段,原始的C和C++描述必須手工轉換為使用VHDL或Verilog HDL。在這個轉換過程中會花費大量的時間,并產生一些錯誤。

其次,當使用C語言描述的模塊轉換成HDL描述的模塊之后,后者將會成為今后設計的焦點,而設計人員花費大量時間建立起來的C模型將再沒有什么用處。

再次,需要使用多個測試平臺。因為在系統級建立起來的針對C語言描述的模塊測試平臺無法直接轉換成針對HDL語言描述的模塊所需要的測試平臺。

2 使用SystemC的必要性

無論采用什么樣的設計方法學,人們都需要對SOC時代的復雜電子系統進行描述,以選擇合 適的系統架構,進行軟硬件劃分,算法仿真等等。描述的級別越低,細節問題就越突出,對實際系統的模仿就越精確,完成建模消耗的時間、仿真和驗證時間就越長。相反,描述的抽象級別越高,完成建模需要的時間就越短,但對目標系統的描述也就越不精確。作為設計人員必須在速度和精確性之間做出選擇。

人們對系統級描述語言的要求是:高仿真速度以及建模效率、時序和行為可以分開建模、支持基于接口的設計、支持軟硬件混合建模、支持從系統級到門級的無縫過渡、支持系統級調試和系統性能分析等。人們迫切需要一種語言單一地完成全部設計。這種語言必須能夠用于描述各種不同的抽象級別(如系統級、寄存器傳輸級等),能夠勝任軟硬件的協同設計和驗證,并且仿真速度要快。這就是所謂的系統級描述語言SLDL,而傳統的硬件描述語言如VHDL和Verilog HDL都不能滿足這些要求。

SystemC就是目前這方面研究的最新、最好的成果,他擴展傳統的軟件語言C和C++并使他們支持硬件描述,所以可以很好地實現軟硬件的協同設計,是系統級芯片設計語言的發展趨勢。

3 SystemC簡介

1999年9月,微電子業內的一些一流的EDA公司、IP提供商、半導體制造商及系統和內嵌式軟件設計公司聯合創建了開放SystemC創始會組織(Open SystemC Intitiative,OSCI),并推出了基于C++的系統級設計語言SystemC。OSCI是一個非盈利性組織,他負責維護和發展SystemC。SystemC是完全免費的,這使得EDA供應商能夠充分自由地了解SystemC庫的源代碼以優化他們的各種解釋工具;包括Synopsys,Cadence,Frontier Design,ARM,Eri ssion,Lucent,Sony,TI等核心成員。目前已經有50多個著名的微電子公司支持該標準[2]。

SystemC本質上是在C++的基礎上添加的硬件擴展庫和仿真核,這使得SystemC可以建模不同抽象級別的(包括軟件和硬件的)復雜電子系統。他既可以描述純功能模型和系統體系結構,也可以描述軟硬件的具體實現。SystemC源代碼可以使用任何標準C++編譯環境進行編譯,生成可執行文件;可以使用綜合工具(如Synopsys SystemC Compiler)將SystemC的寄存器傳輸級描述綜合為Verilog HDL或者VHDL的代碼用于FPGA設計,也可以綜合為EDIF網表用于A SIC設計[3]。

SystemC具有所有硬件描述語言所共有的基本特征,包括模塊、進程、端口和信號等。不同的是,在SystemC中時鐘被單獨定義為一個特殊的信號,這大大簡化了時鐘信號的定義,SystemC還支持具有任意相位關系的多個時鐘。在SystemC中使用了sc_set_tim e_resoluti on()和sc_set_default_time_unit()來定義時間分辨率和時間單位,這與Ve rilog HDL的timescale語法在功能上是等效的。

pic相關文章:pic是什么

c語言相關文章:c語言教程

c++相關文章:c++教程

評論