突破成本限制 半導體業界追尋替代新技術

隨著晶片制造的成本與復雜度不斷提高,使得今年成為半導體產業整并以及尋找替代性技術創記錄的一年。在日前于美國加州舉行的IEEE S3S大會上,舉會的工程師們不僅得以掌握更多絕緣上覆矽(SOI)、次閾值電壓設計與單晶片3D整合等新技術選擇,同時也聽說了有關產業重組與整并的幾起傳聞。

本文引用地址:http://www.104case.com/article/264878.htm截至目前為止,今年全球半導體公司已經完成了23筆收購交易了,這比起過去兩年的交易數總和還更多,摩根士丹利(Morgan Stanley)半導體投資銀行全球負責人Mark Edelstone在發表專題演講時透露。他同時預測今年的全球并購交易總值可能從174億美元增加到近300億美元。

“今年的情況真的是破記錄了!”他列舉了今年出現的幾宗較大整并案例,如英飛凌科技(Infineon Technologies)和國際整流器(IR)公司,以及安華高(Avago)和LSI公司之間的并購交易。“這個趨勢將會延續下去,預計在今后幾年都將呈現非常繁忙的并購景象。”

?

2009-2014年全球半導體產業并購交易數與總額

資金成本較低正為所有的產業掀起并購浪潮,而晶片制造成本和復雜度的增加更助長了半導體產業的并購。目前制造一個20nm晶片的成本約需5,300萬美元,較制造28nm晶片成本所需的3,600萬美元更大幅提高,預計到了16/14nm節點時還將出現另一次躍升的高成本,Edelstone表示。 “要在這樣的投資環境下賺錢,真的需要非常大的市場,而且還會對半導體產業的發展帶來巨大的影響。到了16/14 nm FinFET世代,每閘極成本仍持續地攀升,這將顯著地改變半導體產業現狀——事實是:規模決定成敗。”

與會的多位發言人一致認為,如今在整個產業中,每電晶體成本仍不斷上升中。不過,英特爾(Intel)在今年9月時透露,其14nm FinFET制程將可支援更低的每電晶體成本。

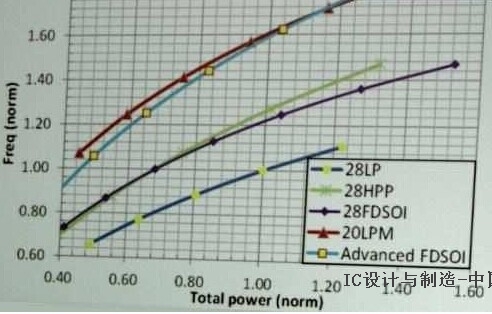

14/16nm FinFET制程節點象征著產業今后發展的主流方向,但完全耗盡型(FD)和極薄的SOI制程也有機會,GlobalFoundries公司產品經理Michael Medicino表示。

有些對成本敏感的行動晶片由于考慮到成本將會避免采用14nm和10nm FinFET制程,而且時間可能長達4至6年。SOI可說是為其提供了另一種替代方案,它能以接近28nm聚合物電晶體的成本,達到20nm bulk電晶體的性能,不過他認為在市場壓力下所有的bulk電晶體成本還會進一步下降。

Mendicino預計SOI替代技術在未來三年中占據約10%的代工業務比重,不過他強調這只是猜測。“三年后再問我吧!”他打趣道。

此外,聯發科(Mediatek)高性能處理器技術總監Alice Wang介紹一個次閾值設計的案例。該公司的遠大目標在于推動晶片達到漏電流和動態能量交會的最小能量點,這同時也是在她的博士論文和ISSCC 2004論文中提出的一個概念。

工程師們已經針對這項艱巨的目標努力了近一年。接下來將面臨的挑戰是提供仍能完成有意義的工作、可靠并且具有最小開銷的晶片,Alice指出。

大規模平行架構有助于提供超低功耗晶片進行媒體處理任務時所需的性能。此外,時序收斂方面的新方法與新工具可以解決一些可靠性和開銷的問題,她表示。

“我認為現在正是讓超低電壓(ULV)成為我們日常生活一部份的時候了。”她在提到開發中市場正出現可穿戴和設計議題時指出,“世界上還有大約13億人——占全球人口的20%,目前都還沒有電力供應……因此能源是新興市場面臨的真正關鍵挑戰。”

?

GlobalFoundries預計,下一代SOI可望以28nm聚合物電晶體的價格提供20nm的性能。

大會主持人Zvi Or-Bach特別提到會議期間舉辦的兩次專題討論,會中討論到如何擴展目前最新快閃記憶體晶片中采用的單晶片3D設計類型。

專題討論之一由來自CEA-Leti和意法半導體(STMicroelectrlnics)的研究人員介紹單晶片3D整合技術,這是因應2D晶片微縮帶來不斷增加的成本而開發的一種替代性技術。他們在一項FPGA案例研究中發現,采用這種技術能夠比傳統堆疊結構減少55%的面積。

在這份研究報告指出:單晶片3D整合技術旨在按上下順序一個接一個地處理電晶體。然而,在實際建置時面臨著許多挑戰,例如在溫度低于600℃的情況下能夠取得高性能頂部電晶體、以便在頂部堆疊式FET制造過程中防止底部FET出現性能退化……固定相位外延再生長已證明其效率包含600℃左右的熱預算,預計在向下變化時也能具有高效率。

另外,EV Group和Nikon公司代表分享用于鍵合與校準系統的新功能細節,這些技術能夠避免目前3D晶片堆疊中使用的矽穿孔(TSV)的高成本和高復雜度。

EV Group公司展示為200nm或更先進制程進行鍵合校準精密度的案例。Nikon介紹了一種新的EGA精密晶圓鍵合技術,“它可以獲得比250nm制程更好的穩定度和更高校準精密度……從而為制造未來的DRAM、MPU和影像感測器等3D IC開路。”

評論