ASIC和SoC設計中嵌入式存儲器的優化

在傳統的大規模ASIC和SoC設計中,芯片的物理空間大致可分為用于新的定制邏輯、用于可復用邏輯(第三方IP或傳統的內部IP)和用于嵌入式存儲三部分。

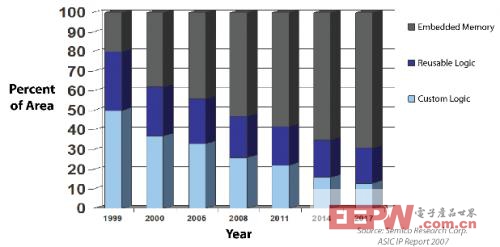

當各廠商為芯片產品的市場差異化(用于802.11n的無線DSP+RF、藍牙和其他新興無線標準)而繼續開發各自獨有的自定義模塊,第三方IP(USB核、以太網核以及CPU/微控制器核)占用的芯片空間幾乎一成未變時,嵌入式存儲器所占比例卻顯著上升(參見圖1)。

圖1:當前的ASIC和SoC設計中,嵌入式存儲器在總可用芯片空間中所占比例逐漸升高。

Semico Research 2013年發布的數據顯示,大多數SoC和ASIC設計中,各式嵌入式存儲器占用的芯片空間已超過50%.此外,許多大規模SoC嵌入式存儲器的使用目的和主要性能也各不相同,如圖2所示。

圖2:多核SoC的各種嵌入式存儲器IP.

由于可以根據設計目的,通過采用正確的SoC存儲器類型來優化設計,因此,對于設計師來說,利用各種存儲器IP具有非常重要的意義。設計師可通過恰當分配各種存儲器IP所占比例,實現速度、功耗、空間(密度)以及非易失性等各種性能參數的優化。

嵌入式存儲器的主要設計標準

各種應用設計中,最佳存儲器IP的確定主要基于以下5個驅動因素,如圖3所示:

1功率

2速度

3可靠性/良率

4密度

5成本

圖3:確定存儲器IP的主要因素。

通過對上述各性能決定要素進行權衡,可得到最優解決方案。許多情況下,存儲器編譯器可根據輸入存儲器設計生成流程中的各種驅動因素,自動生成性能經過優化的特定存儲器IP.同樣重要的是,存儲器IP的支持性結構應適用可靠的驗證方法,且生成的IP良率最高。最后,為實現產量與質量的最優化,存儲器編譯器還應直接生成GDSII,無需人工干預或調整。其他要素還包括良好的設計余量控制、對自動測試圖形向量生成和內建自測試(BIST)的支持。此外,最好具備通過BIST的單步執行進行硅片調試的功能。

評論