臺積電釋放十大信號,對EDA、IP、IC設計和半導體設備商將產(chǎn)生怎樣的影響?

(6)N7和N7+的狀態(tài)

本文引用地址:http://www.104case.com/article/201810/392800.htm從N7節(jié)點的生產(chǎn)到N7+(4層EUV)產(chǎn)品的過渡正在有序進行。N7+的所有EDA參考流程已經(jīng)完全驗證通過,并且PDK迭代到了v1.0。所有基礎IP都通過了硅驗證。IP開發(fā)人員的設計套件已經(jīng)就緒,并且可以接受N7+的新流片。

與N7相比,N7+實現(xiàn)了1.18倍的面積優(yōu)勢,這主要得益于更緊密的金屬間距,以及對單元之間的“通用多器件邊緣”(CPODE)隔離器件的標準單元模板支持。為了有效利用N7+對N7的密度增益,需要重新設計IP-臺積電提供布局遷移輔助工具來協(xié)助這種轉(zhuǎn)變。

值得注意的是,單元管腳形狀可以違反最小金屬區(qū)域光刻設計規(guī)則,管腳單元區(qū)域“修補”涉及的EDA需求可以被整合到物理實現(xiàn)流程中,這需要改變電遷移分析規(guī)則,同時,單元管腳形狀需要和貼片填充的模型一起被提取出來,用于信號的EM分析。

(5)N5工藝支持

臺積電技術(shù)開發(fā)副總裁CliffHou介紹了N5工藝節(jié)點支持計劃:

PDK迭代到了v0.5,IP設計仍在進行中;

臺積電基礎IP通過了硅驗證(比如標準單元、SRAM、eFuse);

v0.9PDK將于2018年11月推出。

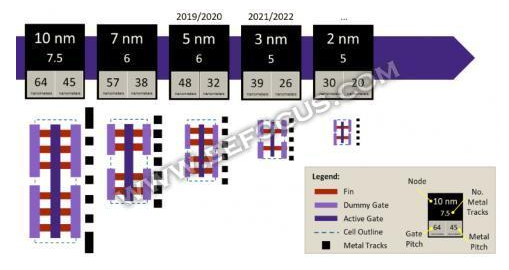

N5標志著引入“全”EUV工藝(比如14個掩膜),可實現(xiàn)對N7的1.86倍面積優(yōu)勢。

讀者應該知道向EUV光刻的過渡面臨不少挑戰(zhàn),比如光源功率、光源正常運行時間、曝光劑量的統(tǒng)計學變化、抗蝕劑靈敏度、掩膜空白缺陷密度和掩膜檢查、薄膜技術(shù)等。不過有趣的是,從N5資格認證計劃中看不出這些EUV挑戰(zhàn)對臺積電時間表的影響。

(4)N5獨特的EDA支持特性-第1部分:3:2節(jié)距比

N5中的metal1(垂直)間距與柵極(垂直)間距的比值為3:2,即3個metal1(M1)垂直軌道相當于2個柵極間距軌道。

此外,M1層需要完整的多重圖案顏色分配,這需要獨特的單元設計,并滿足特殊的單元放置限制和布線要求。正如Synopsys的一位發(fā)言人所指出的那樣,“現(xiàn)在4個中有1個是合格的-這個比例曾經(jīng)是98%。”

單元庫需要包含電等效(EEQ)單元,以支持與整個間距網(wǎng)格的軌道/顏色/引腳形狀對齊。

一些演示稿給出了一些定制電路設計示例,需要增加使用堆疊性的n-高器件和串并聯(lián)的mXn器件。這些器件陣列的布局需要遵守上面提到的間距和顏色分配限制。

(3)N5獨特的EDA支持特性-第2部分:跨行Vt規(guī)則

單元庫一般包含多種變體,邏輯上等同的單元變體可以使用不同的Vt選擇。為了實現(xiàn)功耗/性能的優(yōu)化,可以更換不同的單元,只需對行內(nèi)單元間的Vt選擇做出少許限制。

N5引入了復雜的“跨行”Vt規(guī)則,在EDA上體現(xiàn)為:APR工具、功耗/性能優(yōu)化、填充插入和(特別是)ECO流程。

由于“上下文敏感”的器件漏電-單元內(nèi)的器件泄露電流取決于臨近單元的Vt類型,跨行Vt規(guī)則需要更加嚴謹。這意味著特征化流程的重大變化。單元特征化需要利用多個布局上臨近的單元進行精確的泄露建模。泄露“side文件”模型將通過特征化流程生成,在功耗優(yōu)化階段讀取,以選擇對應于實際物理布局的特定上下文模型。

(2)N5獨特的設計特征-第3部分:P/G設計

N5節(jié)點的標準單元模板電源接地(P/G)網(wǎng)絡設計和之前的節(jié)點又很大不同,它需要更高密度的M1軌(增加30%),相應地也需要更多通孔。

需要注意的是,密度更高的M1P/G網(wǎng)絡也會影響單元布局,因為管腳形狀會被P/G網(wǎng)絡阻擋。

此外,為了幫助緩解N5工藝中由于更高電阻率導致的電源分配網(wǎng)絡動態(tài)電壓降(DvD)問題,并幫助解決由于更高金屬電流密度引起的功率因數(shù)問題,臺積電推出了一種“超高密度”的金屬-絕緣體-金屬(MIM)電容元件,以改善PDN去耦。插入這些新的MIM帽會在APR中引入復雜的布線規(guī)則,并需要新的寄生提取(和LVS)工具功能。

(1)N5獨特的EDA支持特性-第4部分:超低電壓(ULV)延遲建模精度

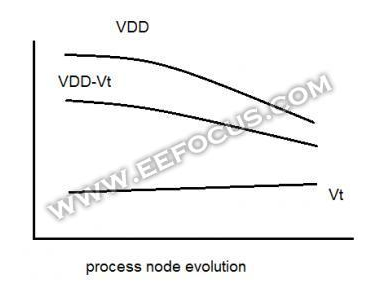

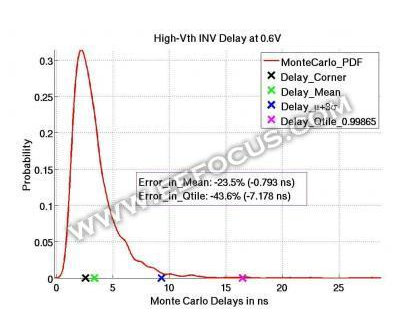

之前,反映統(tǒng)計過程變化的單元弧延遲模型會假定一個對稱的高斯分布(眾數(shù)=中位數(shù)=數(shù)學期望),應用統(tǒng)計靜態(tài)時序分析方法來收斂時序并確保在“n-sigma”處的穩(wěn)健電路性能。現(xiàn)在,越來越多的先進工藝節(jié)點引入了非對稱延遲分布,特別是當VDD供電比設計Vt下降地更快時(因此(VDD-Vt)過驅(qū))。

所以引入了“第二代”單元特征變化格式,以支持分布峰(眾數(shù))兩側(cè)快速和慢速延遲時的獨特西格瑪。

在N5節(jié)點上,統(tǒng)計性延遲分布(在低VDD下)甚至更加陡峭,因此需要對單元延遲變化格式進行進一步更新,尋找新的特征和自由變化模式模型,以反映分布中的附加時刻-即數(shù)學期望、西格瑪和“斜率”。EDASSTA工具需要增強,以支持這種新的庫模型。

額外的器件老化也可能在意外的電路條件下出現(xiàn)。

德州儀器在OIP論壇上的演講中指出,設計人員需要關注器件老化機制(比如HCI/BTI),以及由此產(chǎn)生的對電路性能和EM健壯性的影響。這個演講主要針對的是基于臺積電16FFC工藝的汽車器件市場,但是其中描述的新型模型-應力-老化模擬流程(具有自加熱加速)也適用于任何基于老化的分析。

有一個評論引起了我的注意,“選擇和老化相關的壓力測試條件可能極具欺騙性。最初,我們主要專注于評估含有高速開關活動測試用例的最壞性能路徑。但是,性能最壞和最壞情況下的老化并不等同。由靜態(tài)DC偏置或開關瞬變導致的器件飽和與熱載流子注入密切相關。但是,處于靜止亞Vt條件下的器件-特別是在斷電期間-同樣會受到高應力環(huán)境的影響。一個堆疊器件中的下電器件也可能長時間暴露在高Vds下。我們發(fā)現(xiàn)非導電應力導致的類HCI老化可能是電路參數(shù)漂移的重要原因。設計師需要一定的洞察力識別這些情況,以建立老化模擬測試用例,這可能需要和性能模擬測試分開獨立開發(fā)。”

這個建議不錯。

總結(jié)

臺積電OIP論壇透露的關鍵信息是N7+和N5工藝節(jié)點的進展迅速,而且EUV的引入也不存在太多技術(shù)障礙。N5具有全新的物理和電氣特性,可能會影響單元設計、APR和單元特征化。

可靠性和老化流程在所有細分市場中將變得越來越重要。

臺積電將繼續(xù)和客戶緊密合作,共同開發(fā)先進的封裝技術(shù)。

這些進展都很迅速,這完全得益于臺積電OIP和EDA合作伙伴、IP開發(fā)商的合作模式。

評論