三星VS臺(tái)積電 10nm之后聽誰的

三星10m之后:8nm和6nm

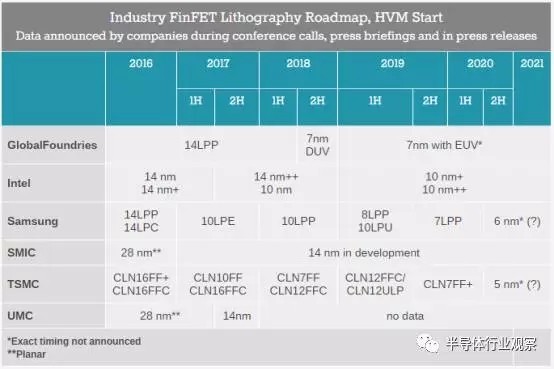

本文引用地址:http://www.104case.com/article/201705/358906.htm三星的7nm制造技術(shù)被認(rèn)為是該公司首個(gè)使用EUV光刻量產(chǎn)節(jié)點(diǎn)。據(jù)報(bào)道,量產(chǎn)時(shí)間會(huì)在2019年或之后,但是試產(chǎn)會(huì)在2018年系半年。但是在接下來的幾年,一切會(huì)變得更加有趣。因?yàn)?a class="contentlabel" href="http://www.104case.com/news/listbylabel/label/三星">三星在Roadmap上公布了之前很少被提到的8nm和6nm制程。

三星官方表示,和現(xiàn)有的節(jié)點(diǎn)技術(shù)相比,這兩個(gè)新技術(shù)將會(huì)提供更好的擴(kuò)展性、性能和功耗優(yōu)勢,這就意味著新技術(shù)相比三星現(xiàn)在正在使用的14nm和10nm工藝性能更好是必然的。最重要的是,三星表示,8nm和6nm節(jié)點(diǎn)會(huì)分別繼承現(xiàn)有的10nm和7nm技術(shù)的優(yōu)勢。這就意味著8nm在一些關(guān)鍵層依舊使用DUV和多次曝光(三次或者四次,但三星方面并沒有確認(rèn)是否會(huì)用四次),而6nm則是三星的第二代EUV技術(shù)。

現(xiàn)在關(guān)于三星8LPP制造技術(shù)唯一確定的是他們會(huì)使用DUV制程技術(shù)去縮小die的尺寸(增加晶體管密度),同時(shí)擁有比10LPP更好的頻率表現(xiàn)。考慮到新工藝對(duì)前任的技術(shù)技術(shù),我們認(rèn)為8LPP會(huì)在2019年帶來更高性能的SoC生產(chǎn)。

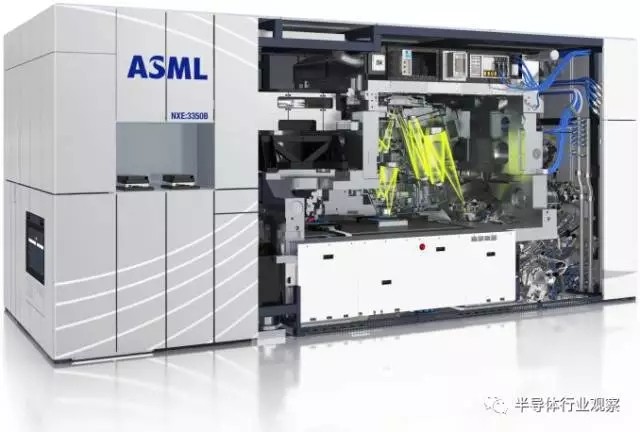

由于三星計(jì)劃在2018年下半年試產(chǎn)7LPP,但直到2019年下半年前,還是沒辦法實(shí)現(xiàn)量產(chǎn)。需要提醒一下,三星現(xiàn)在都是在十月份開始其先進(jìn)工藝的大規(guī)模量產(chǎn),那么就意味著我們也許會(huì)在2019年秋天看到7LPP的大規(guī)模量產(chǎn)。但是8LPP會(huì)是三星當(dāng)年更先進(jìn)的工藝。三星并沒有提及其6nm工藝的時(shí)間線,也沒有透露太多關(guān)于此技術(shù)的信息。但我們可以肯定的是需要使用ASML的EUV工具(例如NXE:3350B)去處理更多的圖層,以求獲得更好的PPA。而據(jù)我們估計(jì),真正的量產(chǎn)時(shí)間會(huì)在2020年之后。

在今年三月,三星只是簡單提了一些他們的10LPU、8LPP和6nm制程技術(shù),但他們并沒有談及太多技術(shù),甚至連PPA的提升目標(biāo)也沒有講到。增加了兩個(gè)DUV技術(shù)節(jié)點(diǎn)(10LPU和8LPP)意味著到2019至2021年間,EUV不會(huì)是所有應(yīng)用的最好選擇,這是非常合乎邏輯的。那么問題就回到,我們不知道DUV和EUV在EUV早期應(yīng)該以一種怎么樣的方式共存。

五月底,三星將會(huì)在美國舉辦FAB論壇,屆時(shí)我們也許會(huì)有更多機(jī)會(huì)去了解三星在FAB方面的計(jì)劃。但我們?nèi)绻氲玫礁嚓P(guān)于這些新技術(shù)的細(xì)節(jié),也許還需要多等幾個(gè)月。

所以現(xiàn)在我們來討論一下那些沒那么先進(jìn)的技術(shù)吧,每年使用這些技術(shù)的產(chǎn)品銷量都會(huì)高達(dá)數(shù)億顆。

并不是每個(gè)人都需要先進(jìn)工藝:TSMC 22 nm ULP、12nm FFC和12 nm FCC+

現(xiàn)在,讓我們討論一下那些沒那么先進(jìn),但是被銷量巨大產(chǎn)品采用的技術(shù)。

開發(fā)基于FinFET技術(shù)的芯片比平面晶體管貴得多,制造成本會(huì)高昂得多。事實(shí)上,F(xiàn)inFET也根本不適合那些需要多樣化方案的物聯(lián)網(wǎng)相關(guān)芯片開發(fā)者。

GlobalFoundries 和Samsung給他們提供了FD-DOI工藝。這個(gè)公司除了有更好的成本優(yōu)勢外,還有其他方面的優(yōu)點(diǎn)。TSMC也打算為這些應(yīng)用推出一個(gè)全新的22nm ULP工藝。CLN22ULP是該公司28nm HPC+工藝的一個(gè)優(yōu)化版本。相比于28nmHPC+,22ULP能降低10%的面積,提升15%的性能,功耗也能降低35%。22ULP是TSMC ULP家族的另一個(gè)新成員,這會(huì)和GlobalFoundries的22FDX和三星28nm FD-SOI競爭。

接下來就是TSMC 的CLN12FFC制造技術(shù),這是該公司CLN16FFC工藝的優(yōu)化版本,能降低20%的面積。可以看到的是,能帶來更高的晶體管密度。

CLN12FFC在相同功耗的情況下提供10%的頻率提升;而在時(shí)鐘頻率相同的情況下,能帶來25%的功耗減少。從Roadmap我們可以看到,TSMC技術(shù)啊提供一個(gè)擁有更低電壓的CLN12FFC,但這到2018或者2019年,都不會(huì)實(shí)現(xiàn)。

評(píng)論