三星VS臺積電 10nm之后聽誰的

2017年3月,三星和臺積電分別就其半導體制程工藝的現狀和未來發展情況發布了幾份非常重要的公告。三星表示,該公司有超過7萬個晶圓加工過程都采用了第一代10nm FinFET工藝,未來這一數量還會繼續增加,同時,三星還公布了未來的即將采用的工藝路線圖。特別是,三星計劃在未來將公布三個工藝,目前為止,我們對于這三個工藝均一無所知。

本文引用地址:http://www.104case.com/article/201705/358906.htm另一方面,臺積電表示,采用其第一代10nm工藝的芯片將會很快實現量產,同時,臺積電也表示,在未來幾年,臺積電將會陸續推出幾項全新的工藝,這其中就包括將在2019年推出的首款7nm EUV工藝。

10 nm: 三星還在不斷推進

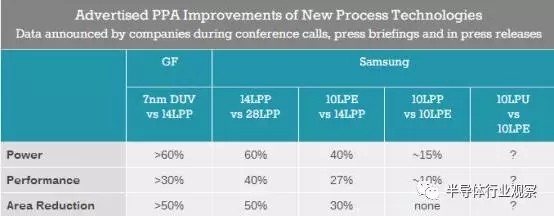

眾所周知,2016年11月份,三星已經開始將10LPE制造技術應用到其生產的SOC中。這一制造技術與三星之前使用的14LPP工藝相比,將能夠縮小30%的晶片面積,同時能夠降低40%的功耗或者是提高27%的性能(以同樣的能耗)。到目前為止,三星已經用該技術加工量超過七萬片wafer,從這一過程中規可以大概估算出三星的技術(考慮到10nm的工藝生產周期為90天左右)。

同時,我們應當知道的是,三星目前還沒有推出很多10nm工藝的產品:只有三星自己的Exynos系列和三星為高通代工的835芯片是使用了三星的10nm工藝。

除了以上產品之外,三星計劃在2017年底量產采用第二代10nm工藝的芯片,也就是三星所說的10LPP工藝。未來,三星將會在2018年底推出采用第三代10nm工藝的芯片(10LPU)。去年,三星曾表示,10LPP工藝比現有的10LPE工藝提高了10%左右的性能,而10LPU工藝,具體細節目前還一無所知。

但是我們可以肯定的是10LPU工藝必然在性能,功耗和芯片面積上有所提升,但是具體在哪一方面會有巨大突破,目前還不甚明朗。

隨著這一工藝的出現,三星也將會和Intel在14nm上推出三代不同的改進工藝一樣,在10nm上推出三種不同的改進工藝。

不過值得注意的是,三星在14nm上并沒有推出14LPC工藝的產品,那么我們可以猜測,在10nm上,三星也不會推出對應工藝的產品。

這是否意味著,三星推出的10LPU工藝主要針對的是超小型的、超低功耗的應用各種新興應用呢,三星還沒有給出確切的回答。

10nm: TSMC已經準備好了

至于臺積電,其10nm工藝(CLN10FF)已經有兩個工廠能夠達到合格要求,其大規模量產大概時間為2017年下半年。預計未來這兩個工廠每季度能夠生產上萬片芯片。臺積電希望能夠不斷增加產能,計劃在今年出貨40萬片晶圓。

考慮到FinFET技術冗長的生產周期,臺積電想要提高10nm工藝的產能來滿足其主要客戶的芯片需求,還需要很長的產能爬坡時間。那么蘋果如果想要使用采用這一工藝的芯片,為其今年九月或者是十月推出新手機進行大量備貨,在前期還是非常困難的。

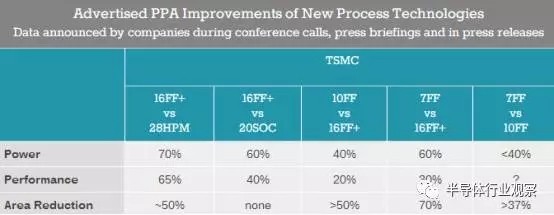

CLN10FF技術與CLN16FF+技術相比到底存在多少優勢在臺積電內部已經進行過多次討論,該工藝明顯是針對移動設備使用的SOC的,而不是為普通的芯片廠商準備的。在相同的功率和復雜性下,該工藝能夠提高50%的芯片密度。如果采用同一頻率和復雜性,同時降低40%的功耗,同樣能夠帶來20%的性能提升。

與三星不同的是,臺積電并不打算在10nm工藝上推出多個改進型工藝。臺積電預計在明年直接推出7nm工藝。

7nm對于半導體制造工藝來說是非常重要的里程碑,吸引了很多設計者為之努力。

但是,臺積電的野心明顯不止于此,臺積電未來還打算推出多種專門針對超小型和超低功耗應用的制造工藝。

超越10nm的臺積電:7 nm DUV 和 7 nm EUV

如前所述,未來臺積電的7nm工藝將會被應用到數百家公司的數以千計的不同的應用之中。

不過,臺積電最初的計劃并不是這樣。臺積電最初為7nm工藝設計了兩個版本:一種是針對高性能應用的7nm工藝,一種是針對移動應用的7nm工藝。但是這兩種工藝都需要采用浸沒式光刻技術和DUV技術。經過多次嘗試之后,臺積電最終決定引入更加先進的制造工藝,將EUV技術引入7nm工藝中。這一方法可以說是從GlobalFoundries的制造工藝中得到的借鑒。

臺積電的第一代CLN7FF預計將會與2017年第二季度進入試產階段,今年晚些時候可能推出樣片。而大規模的進行生產則需要等到2018年第二季度。所以,我們如果想要在產品中見到采用7nm工藝的芯片產品,至少需要等到明年下半年。

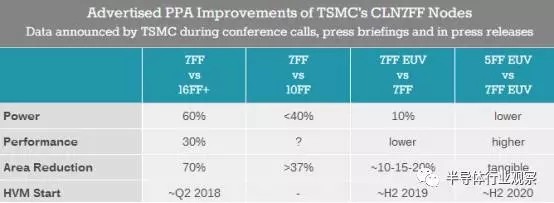

與CLN16FF+相比,CLN7FF工藝將會使得芯片制造上在相同晶體數量的情況下,整體的體積縮小70%;而在相同的芯片復雜性情況下,將能夠降低60%的功耗或者是增加30%的頻率。

據了解,臺積電未來推出的第二代7nm工藝(CLN7FF+),將會引入EUV技術,這就要求開發出針對7nm工藝重新設計的更多的EUV生產規則。改進后的工藝預計可能縮小10-15~20%左右的晶圓面積,同時能夠提高性能,降低功耗。

此外,與傳統的生產設計工藝相比,使用DUV工具進行設計,能夠極大的縮短生產周期。

臺積電第二代7nm工藝(CLN7FF+)預計將于2018年第二季度進行試產,2019年下半年能夠量產面市。

事實上,三大代工廠商在7nm工藝節點上都將會是使用EUV技術。但是ASML和其他EUV設備上想要真的將EUV技術投入商業應用,至少還需要兩年的時間。

雖然在某些方面EUV可以實現,但是要真的應用還需要等到2019年。但是,臺積電和三星都已經在討論第二代EUV工藝了,從目前的情況來看,代工廠商對于EUV廠商的未來的設備進度還是抱有非常大的信心的。

評論