【E問E答】半導(dǎo)體新制程節(jié)點定位命名誰說的算數(shù)?

半導(dǎo)體制程節(jié)點名稱出現(xiàn)前所未有的“增生”情況,產(chǎn)業(yè)界需要一種優(yōu)良的公用性能基準,才能對不同業(yè)者的半導(dǎo)體制程技術(shù)進行比較。

本文引用地址:http://www.104case.com/article/201704/346596.htm這段時間以來,晶圓代工業(yè)者紛紛將他們自己的最新制程節(jié)點以自己想要的市場定位來命名,并非依據(jù)任何透明化的性能基準,而現(xiàn)在該是時候阻止這種“欺騙”行為。

英特爾(Intel)最近提出了一種簡單、但在某種程度上有點“自私自利”的電晶體密度量測標準,其他晶圓代工競爭對手則以“震耳欲聾的沉默”回應(yīng);筆者猜測,這是因為英特爾的電晶體密度確實具備領(lǐng)先水準,而這是其他競爭者不愿意承認的。

最近英特爾決定公開10納米制程包括鰭片(fin)間距、高度與最小金屬/邏輯閘間距等量測數(shù)據(jù);雖然該節(jié)點還未開始量產(chǎn),但這個行為值得稱贊。上述量測數(shù)據(jù)是所有的晶圓代工廠在首度發(fā)表一個新制程節(jié)點時,應(yīng)該要提供的基本細節(jié)。

不過,從這類量測數(shù)據(jù)與電晶體密度衍生出的資訊無法窺得制程性能之全貌──如果無法讓電晶體支援明顯更高的速度或更低的功耗,無論它們密度有多高都沒用。

時間倒回2009年,當(dāng)時ARM的技術(shù)長Mike Muller創(chuàng)造了“暗矽(dark silicon)”這個新名詞,表示根據(jù)他的觀察,工程師們正往裸晶上納入更多電晶體,但缺乏能讓眾多電晶體開啟的電源預(yù)算(power budget)。

英特爾的電晶體密度量測還有進步的空間,因為缺乏相關(guān)聯(lián)的性能/功率方程式,還是無法讓人縱覽全局;在過去幾年,產(chǎn)業(yè)界已經(jīng)采納了用PPA指標──性能(performance)、功耗(power)與面積(area)──來量測半導(dǎo)體制程節(jié)點。

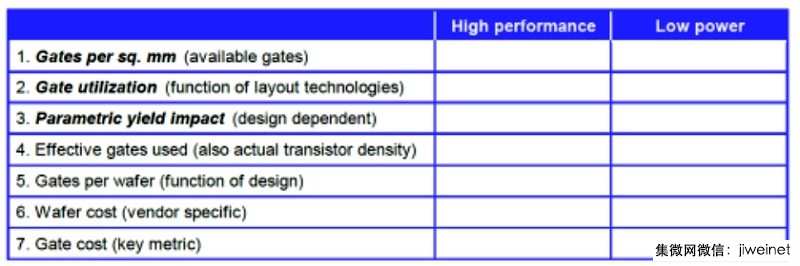

對此產(chǎn)業(yè)顧問機構(gòu)International Business Strategies (IBS)建議,以“有效邏輯閘(effective gates)”做為量測基準;該機構(gòu)執(zhí)行長Handel Jones解釋,有效邏輯閘就是計算可用的邏輯閘數(shù)(英特爾的量測包含此項),還有邏輯閘利用率與良率。

但他也指出,雖然可用邏輯閘數(shù)對量測制程性能有幫助,仍只能顯現(xiàn)“冰山的一角”,其中的困難在于:“廠商對于良率資訊非常保密,除非是單閘成本(cost per gate);但良率是非常關(guān)鍵的量測指標,會受到缺陷率(D0)以及參數(shù)性/系統(tǒng)性(parametric/ systemic)良率影響。”還關(guān)系到客戶會花多長的時間拿到芯片。

針對英特爾提出的制程量測基準,有幾位讀者提供了他們的看法;有一位讀者呼吁以奈秒(nanoseconds)/mm2為單位的RC時間延遲做為基準:“如果我們使用每單位長度的電容與電阻。”另一位讀者則認為,英特爾的量測基準并不實用,因為并沒有包括標準單元軌(standard cell tracks)資訊。

還有讀者表示,真正的量測應(yīng)該是制程加上程式庫共同運作的表現(xiàn),以及各種設(shè)計類型的性能標準:“我會想知道在實際的合成設(shè)計,像是大型ARM核心或x86核心SoC,在相同的時脈速率下,英特爾的程式庫/制程,與ARM/臺積電(TSMC)程式庫/制程的比較。”

有多位讀者都同意,最終每個節(jié)點的性能表現(xiàn),還是得在以該制程生產(chǎn)的芯片銷售到市場上之后才能被實際檢驗;他們也觀察到臺積電與三星(Samsung)今年準備量產(chǎn)他們稱為7納米的制程,而英特爾則是量產(chǎn)該公司稱為10納米的制程。

資深市場分析師Linley Gwennap表示,英特爾的電晶體密度量測應(yīng)該要與SRAM單元尺寸綜合,才能顯示完整的SoC尺寸全貌,特別是包含大量記憶體的處理器;他也呼吁晶圓代工業(yè)者應(yīng)該提供有關(guān)他們制程節(jié)點的更多資料。

IBS建議芯片設(shè)計業(yè)者在選擇制程時考量此表格中的量測基準(來源:IBS)

越來越多的制程選項讓芯片業(yè)者霧煞煞

目前半導(dǎo)體產(chǎn)業(yè)界對晶圓代工制程性能量測基準的迫切需求是前所未見;像是在3月,臺積電就發(fā)表了三種新制程:22納米、12納米以及7+納米,此外該公司還有多種現(xiàn)有的16納米節(jié)點與10納米節(jié)點制程技術(shù)選項準備在今年量產(chǎn)。身為晶圓代工產(chǎn)業(yè)龍頭的臺積電想要以多種選項通吃市場,但有時只能硬擠出個位數(shù)字的性能提升。

在此同時,另一家晶圓代工業(yè)者Globalfoundries的22納米FD-SOI制程受到各家媒體熱烈報導(dǎo),甚至刺激英特爾從最尖端制程節(jié)點往后退了幾步、發(fā)表低功耗22納米FinFET制程。

晶圓代工大廠們約會在2020年開始采用極紫外光(EUV)微影技術(shù),而來自不同廠商的首批EUV制程可能會有很大差異,端看他們?nèi)绾尾捎眠@種關(guān)鍵新工具。因此,無晶圓廠芯片設(shè)計業(yè)者,需要一種透明化方法來比較各種制程選項的優(yōu)缺點。

然而,活躍于這個領(lǐng)域的產(chǎn)業(yè)組織,如GSA、SEMI與IEEE等,似乎并沒有在這方面做任何努力;其中代表無晶圓廠芯片業(yè)者的GSA特別應(yīng)該要率先挺身而出,但針對此一議題,筆者嘗試聯(lián)絡(luò)幾位GSA代表,到目前為止都還沒有收到回應(yīng)。

可以理解這是一個高度競爭的產(chǎn)業(yè),因此充斥著各種商業(yè)機密;到目前為止,高通(Qualcomm)婉拒了筆者想了解該公司如何比較制程技術(shù)的采訪,Nvdia與聯(lián)發(fā)科(MediaTek)也沒有回應(yīng)我的采訪邀約。這并不令人驚訝,他們可以借由“明智地”選擇制程技術(shù),取得不想放棄的戰(zhàn)略優(yōu)勢;在很多案例中,商業(yè)標準與技術(shù)標準的重要性可能是差不多的。

當(dāng)蘋果(Apple)選擇臺積電做為應(yīng)用處理器代工伙伴,三星一年損失的訂單金額高達數(shù)千萬美元;但有趣的是,幾乎在同一時間,高通開始委托三星以14納米與10納米制程,生產(chǎn)其多款Snapdragon處理器,而且三星成為第一家采用10納米Snapdragon 835芯片的手機業(yè)者(在Galaxy S8智慧型手機)。

半導(dǎo)體制造會牽涉到高科技領(lǐng)域中最復(fù)雜的技術(shù)-商業(yè)決策,影響范圍涵蓋廣泛的系統(tǒng)、軟件與全球各地的服務(wù)市場。但這個產(chǎn)業(yè)需要一些公用的性能量測基準,以理解不斷增生的制程技術(shù)選項;晶圓代工業(yè)者需要負起責(zé)任,提供相關(guān)量測指標數(shù)據(jù)。

英特爾對10納米制程細節(jié)與電晶體密度數(shù)據(jù)的公布是一個開始,其他晶圓代工大廠應(yīng)該要跟進,并繼續(xù)邁出大步,提供制程相關(guān)性能與功耗等量測基準;但筆者并不預(yù)期廠商們會這么做,除非他們確實面臨到壓力。而現(xiàn)在該是像GSA等組織或任何其他人站出來發(fā)聲,打破沉默的時候了!

評論