基于VHDL的線性分組碼編譯碼器設計

1 線性分組碼

分組碼是由一組固定長度為n,稱之為碼字的矢量構成的。線性分組編碼時,將每k個信息位分為一組獨立處理,按一定規則給每個信息組增加(n-k)個監督碼元,組成長度為n的二進制碼字,這種編碼方式記為是(n,k)分組碼。信息位和監督位采用的關系式由一組線性方程所決定,稱之為線性分組碼。

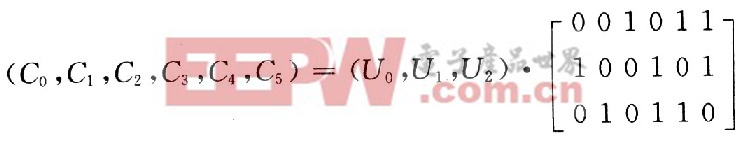

若線性分組碼的輸入信息位為U=(U0,U1,…,Uk),編碼輸出為C=(C0,C1,…,Cn),則有如下關系:

式中:G為線性分組碼的生成矩陣;H為監督矩陣。當G確定后,編碼的方法就完全確定了,而H給定后,編碼時監督位和信息位的關系也就確定了。因此,在設計分組碼編碼器時,需要確定生成矩陣G;在設計分組碼譯碼器時,需要確定監督矩陣H。

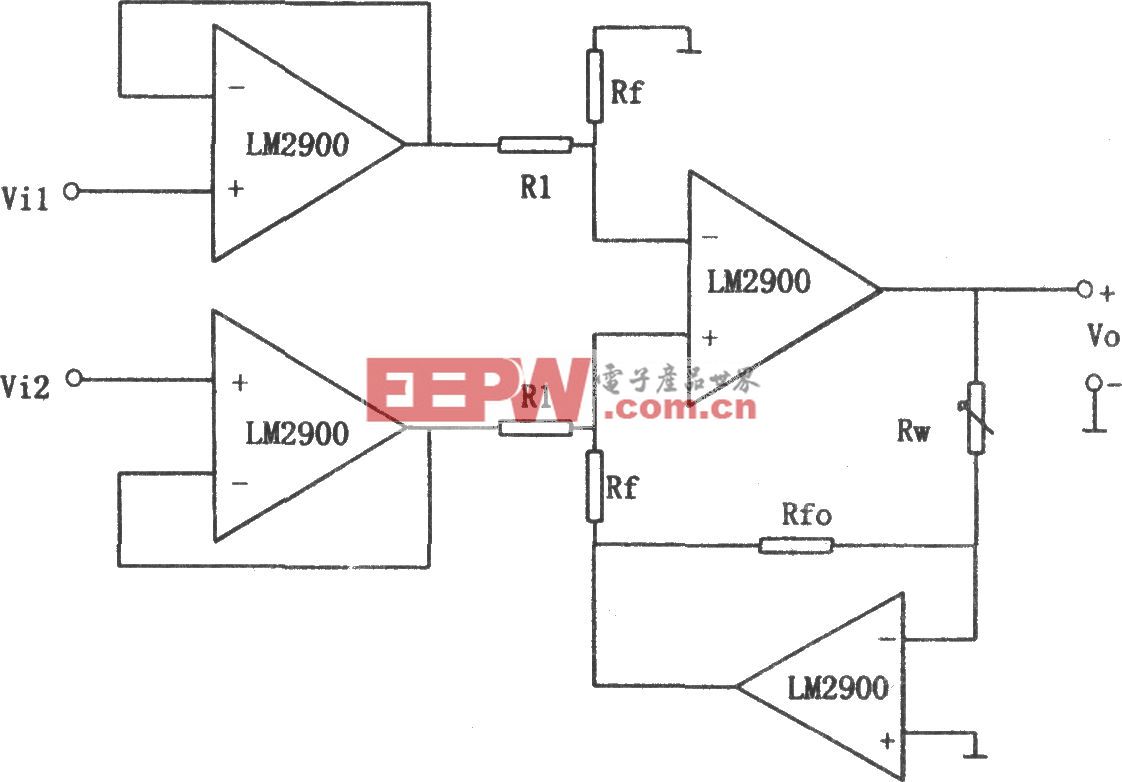

2 線性分組碼編譯碼器設計

2.1 線性分組碼編碼器設計

設

,由于生成矩陣G是k行n列,所以k=3,n=6,改(n,k)碼為(6,3)碼。根據生成矩陣和式(1)運算后得到相應的編碼。即由:

,由于生成矩陣G是k行n列,所以k=3,n=6,改(n,k)碼為(6,3)碼。根據生成矩陣和式(1)運算后得到相應的編碼。即由:

可得:

COUT=(C0,C1,C2,C3,C4,C5)為編碼輸出,其中前3個分量為增加的監督碼元,后3個為原輸入信息位。

評論