一文看懂VHDL和Verilog有何不同

當前最流行的硬件設計語言有兩種,即 VHDL 與 Verilog HDL,兩者各有優劣,也各有相當多的擁護者。VHDL 語言由美國軍方所推出,最早通過國際電機工程師學會(IEEE)的標準,在北美及歐洲應用非常普遍。而 Verilog HDL 語言則由 Gateway 公司提出,這家公司輾轉被Cadence所購并,并得到Synopsys的支持。在得到這兩大 EDA 公司的支持后,也隨后通過了 IEEE 標準,在美國、日本及中國臺灣地區使用非常普遍。

本文引用地址:http://www.104case.com/article/201811/394035.htm我們把這兩種語言具體比較下:

1.整體結構

點評:

兩者結構基本相似,并行語句的種類也類似;

VHDL語言需要進行大量說明,程序通常比較長;

Verilog HDL通常不進行說明,或只進行非常簡短的說明,程序比較簡短。

2.數據對象及類型

VHDL

常量 信號 變量 9種預定義類型 各類用戶定義類型

可描述各類不同的量

必須進行類型說明

運算時必須考慮類型的一致性和適用性

Verilog HDL

常量: 數量,參量

變量:網絡型 寄存器型

類型種類少

運算時所受的約束少

3.運算符號

運算主要分為3類 : 算術運算 邏輯運算 關系運算

算術運算

VHDL中有10種 但很多都不能進行綜合,只能用于行為描述

Verilog HDL中只有能夠綜合的5種

邏輯運算

VHDL中 有常用的6種,均用字符形式表達

Verilog HDL中有3類共14種,

分為一般邏輯運算,位邏輯運算,縮減邏輯運算

關系運算

VHDL中有6種

Verilog HDL中有2類共8種,對比增加了全等和不全等(用于對不定態比較)。

除了以上3類運算外,VHDL中還有連接運算,Verilog HDL中還有連接運算、移位運算和條件運算。

點評:

VHDL的運算劃分比較抽象,適應面較廣

Verilog HDL的運算劃分比較具體,對邏輯代數反映更細致一些。

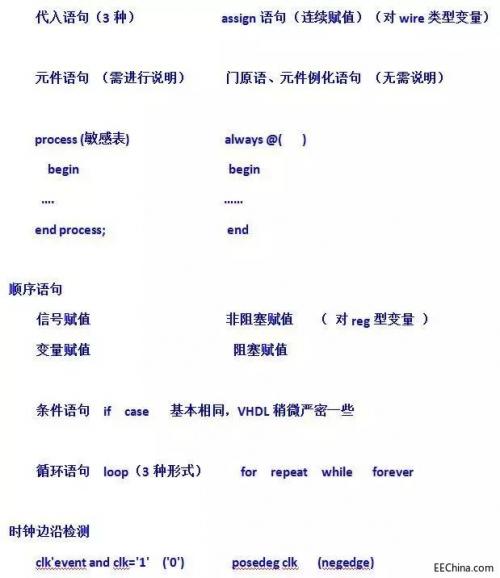

4.語句

兩種語言的語句都分為并行語句和順序語句,并行語句在主程序中使用,順序語句只能在子結構中使用;

并行語句都分為3種形式:

評論