基于VHDL邏輯電路設計與應用

1、引言

本文引用地址:http://www.104case.com/article/201807/384180.htm電子產品隨著技術的進步,更新換代速度可謂日新月異。EDAI'輝lectronicDesignAutomatic)技術的應用很好地適應了這一特點。通過設計和編程,由可編程邏輯器件CPLD/FPGAn-構成的數字電路,取代了常規的組合和時序邏輯電路,實現了單片化,使體積、重量、功耗減小,提高了可靠性。

目前EDA技術在一般的數字系統、數字信號處理系統等領域獲得廣泛應用,它將成為今后電子設計的主流。VHDL語言作為可編程邏輯器件的標準語言描述能力強,覆蓋面廣,抽象能力強,應用越來越廣泛。VHDL語言具有多層次描述系統硬件功能的能力,可以從系統的數學模型直到門級電路,其高層次的行為描述可以與低層次的RTL描述和結構描述混合使用;設計者可以實現從文本編輯、功能仿真、邏輯綜合、布局布線、時序仿真到編程下載整個開發過程,大大減輕了設計人員的工作強度,提高了設計質量,減少了出錯的機會。下面介紹如何在美國ALTERA公司的MAX+PLUSH平臺上應用VHDL實現串行加法器。

2、串行加法器設計原理

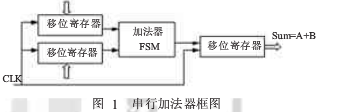

多位串行加法器的工作原理閻是從最低位開始逐位相加并向高位進位,基于這個原理,采用移位加法實現串行加法器。設兩個無符號數A=a-tart...ao和B=b.-,b,^...bo,兩者相加產生的和SUM=S-lS-:...So,其工作原理如圖1所示,由三個移位寄存器和一個加法器有限狀態機組成,其中三個寄存器用來存放A,B和Sum數據。其工作原理是,假定輸人移位寄存器有并行加載功能,首先把A,B的值加載到寄存器,然后在每一個時鐘周期,通過加法器有限狀態機將相應的一位相加,在時鐘周期的結尾處將這一位相加結果移到Sum寄存器。三個寄存器都采用同步正邊沿觸發器,所有變化都在時鐘正邊沿之后很快發生,這時三個寄存器的內容都向右移,將已得到的和位移到Sum,并把兩個加數寄存器的下一個位a與b:送給加法器有限狀態機。

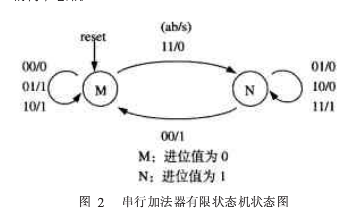

加法器有限狀態機的工作原理:由兩個狀態M和N分別表示進位值0和10狀態圖如圖2所示,采用有限狀態機的Mealy模型。由于每一位相加,都是由全加器構成的,因此根據狀態圖可寫出次態全加器的邏輯表達式:

Y=ab+ay+by

s=a+b+y

其中y為進位輸人,a和b為兩個輸人數據,Y為進位輸出,s為全加器的和。串行加法器可以實現任意位數據加法的簡單電路。

3、基于VHDL串行加法器的實現

串行加法器的VHDL描述由移位寄存器和加法器有限狀態機組成。可以把移位寄存器作為一個子電路,在主程序中可以多次調用。

3.1移位寄存器實現

下面是4位移位寄存器的VHDL代碼,采用FOR LOOP結構來實現,源程序如下:

LIBRARYIEEE;

USEIEEE.STD-LOGIC-1164.ALL;

ENTITYshiftIS GENERIC(n:INTEGER:=4);

PORT(r:INSTD-LOGIC-VECTOR(n-1DOWNTO0);

1,e,w:INSTD-LOGIC;

clk:INSTD_LOGIC;

q:BUFFERSTD-LOGIC-VECTOR(n-1DOWNTO0));

ENDshift;

ARCHITECTUREbehaOFshiftIS

BEGIN

PROCESS

BEGIN

WATTUNTILclk'EVENTANDclk='1';

IFe='1'THEN

IF1='l'THEN

q=r,

ELSE

gebit:FORiIN0TOn-2LOOP

q(i)=q(i+l);

END LOOP;

q(n-1)=w;

ENDIF;

ENDIF;

ENDPROCESS;

ENDbeha;

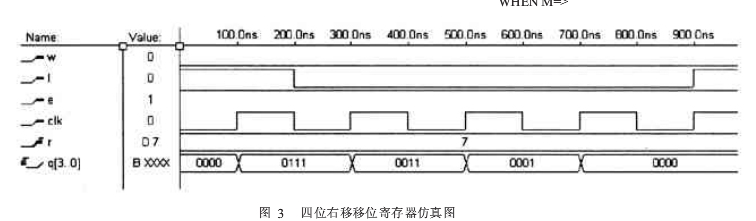

若要實現更多位移位寄存器,則只要修改n值即可。程序中r是輸人信號,clk是時鐘信號,e是使能端。當1='1’時對移位寄存器并行加載,卜'0’時,寄存器處于右移狀態,串行數據從輸人端w移人寄存器的最高位。仿真結果如圖3所示。

3.2串行加法器的VHDL設計

八位串行加法器VHDL代碼如下:

LIBRARYIEEE;

USEIEEE.STDLOGIC-1164.ALL;

ENTITY adderIS

GENERIC(length:INTEGER:=8);

PORT(erset:INSTDLOGIC;

clk:INSTD-LOGIC;

a,b:INSTD-LOGIC-VECTOR(length-1DOWNTO0);

co:outSTD-LOGIC;

sum:BUFFERSTD-LOGIC-VECTOR(length一1DOWNTO0));

ENDadder;

ARCHITECTUREbehaOFadderIS COMPONENTshift

GENERIC(n:INTEGER:=4);

PORT(r:INSTD-LOGIC-VECTOR(n-1DOWNTO1,e,w:INSTD-LOGIC;

elk:INSTD-LOGIC;

q:BUFFERSTD-LOGIC-VECTOR(n-1DOWNTO0));

ENDCOMPONENT;

SIGNALga,gb,null-in:STD_LOGIC-VECTOR(length-1DOWNTO0);

SIGNALs,low,high,run:STD-LOGIC;

SIGNALcount:INTEGERRANGE0TOlength;

TYPEstate-typeIS(M,N);

SIGNALy:state-type;

BEGIN

low='0';

high二,1';

shiftA:shiftGENERICMAP(n=>length)PORTMAP(a,erset,high,low,clk,ga);

shiftB:shiftGENERICMAP(n=>length)PORTMAP(b,reset,high,low,clk,gb);

adderFSM:PROCESS(erset,clk)BEGIN

IFerset='l'THEN

y=M;

ELSIFelk'EVENTANDclk='1'THEN

CASEyIS

WHENM=>IF(qa(0),1'ANDqb(0)='1')THENy=N;

ELSE

y=M;

ENDIF;

WHENN=>

IF(ga(0)='0'ANDqb(0)='0')THENy-M;

ELSE

y=N;

ENDIF;

ENDCASE;

ENDIF;

ENDPROCESSadderFSM;

WITHySELECT

s-ga(0)XORqb(0)WHENM,

NOT(ga(0)XORqb(0))WHENN;

Null_in二(OTHERS=>'0');

shiftsum:shiftGENERICMAP(n=>length)

PORTMAP(nulin,erset,run,s,clk,sum);

stop:PROCESS

BEGIN

WAITUNTIL(elk'EVENTANDclk='1');

IFerset='1'THEN

count=length;

E,ISIFrun='l'THEN

count=count-1;

ENDIF;

ENDPROCESS;

run='0'WHENcount-OELSE'1';

co一out:PROCESS

BEGIN

WAITUNTIL(clk-EVENTANDclk='1');

IFy=MTHEN

co=,0';

EISE

co=,1';

ENDIF;

ENDPROCESScoout;

ENDbeha;

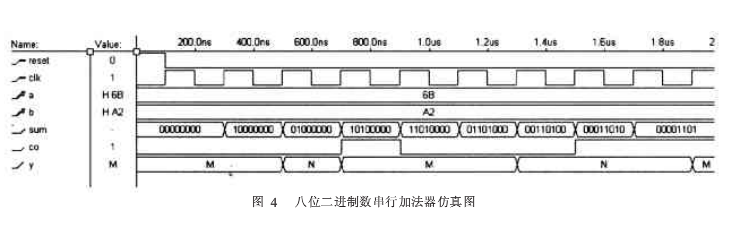

程序中采用三個進程描述:adderFSM進程描述加法器有限狀態機;stop進程描述減法計數器,用來決定加法器什么時候由于n位所要求的和出現在輸出移位寄存器而停止;co-out描述進位co輸出。

程序經Max+PlusII中的Compiler編譯,再通過Simulator和Timinganalyzer工具分別進行功能仿真和時序仿真,仿真結果如圖4所示,其中reset是輸人控制端,clk是時鐘信號,a和b是輸人數據,sum是和數,co是進位,y表示有限狀態機的狀態。仿真正確后,可通過計算機并口上的Byteblaster下載電纜將生成的配置文件直接下載到芯片MAXEPM7128SLC84-15進行驗證,測試結果與實際相符。

4、結束語

本文通過串行加法器VHDL設計表明,VHDL在邏輯電路的設計中具有以下優點:

(1)VHDL語言硬件描述能力強、設計方法靈活;(2)設計者只需掌握VHDL語言及相關EDA設計軟件的使用,而不需考慮較多的硬件結構就可以設計所需要的數字系統;(3)隨時可對設計內容進行仿真,查驗系統功能;(4)程序可移植性強、易于修改;因此,隨著集成電路技術的高速發展,作為當代電子設計人員,HDL已成為設計數字硬件時常用的一種重要手段。

評論