VHDL語言實現的幀同步算法

1 工作原理

實現幀同步的基本方法是在發送端預先規定的時隙,即幀同步碼時隙,插入一組特殊碼型的幀同步碼組。在接收端利用同步碼的自相關性確定幀的同步位置。幀同步碼組可以是集中插入的,也可以是分散插入的。對于分散的幀同步碼插入方式,其工作原理與集中插入方式相類似,下面就以集中插入幀同步碼為例來說明幀同步的工作原理。

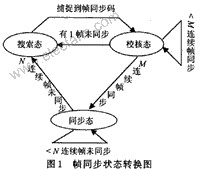

幀同步過程有搜索態、校核態和同步態。其狀態轉換圖如圖1所示。

|

搜索態 在數據接收的起始時刻或幀未同步時,幀同步進入搜索態。在數據流中尋找幀同步碼(111lOlOOOO);當數據流與幀同步碼相同時,表明已搜索到一個同步幀頭;可啟動進入幀同步的校核狀態。

校核態 為了防止信號中出現虛假同步;找到第1組同步碼后跳過1幀長度必須再次確認幀同步碼。若連續經過M幀同步碼確認均同步正確,則系統立即轉入同步狀態;否則存在假同步;返回搜索態。由首次搜索到幀同步頭到進入同步態的M幀時叫后方保護時間。

同步態 幀同步處于同步狀態時;若連續N幀幀同步正確則仍保持在同步狀態。考慮到接收的數據流幀同步碼可能受外界干擾而存在誤碼,在同步狀態中只有連續N幀丟失同步碼才進入失步狀態,并返回搜索態。其中N幀時叫前方保護時間。由于有前方保護時間,在接收過程中雖然出現某幀同步碼誤碼,但系統并不會立即進入失步狀態。由此可減少因誤碼而進入失步狀態的可能性。

2 幀同步實現

我們VHDL語言實現了幀同步的設計,設計程序如下:

首先對相關參數進行定義:

type state_type is (s0,s1,s2);

//系統狀態(搜索態、校核態、同步態)

constant syn_code:bit_vector:=110100; //幀同步碼

constant syn_code_length:integer:=6; //幀同步碼長度

constant max_m:integer:=2; //前方保護幀數

constant max_n:integer:=3; //后方保護幀數

variable m:integer range 0 to max_m:=0;

//連續獲取同步碼數

variable n:integer range 0 to max_n:=0;

//連續丟失同步碼數

variable reg:bit_vector(syn_code_length downto 1);

//移位寄存器

variable state:state_type:=s0; //初始狀態

其次,把接收到的數據送人移位寄存器,并對送人的數據同步碼檢測。當系統處于不同狀態時,其狀態轉換如下:

(1)在搜索態,其VHDL語言描述如下:

if(clk'event and clk='1')then

case state is

when so=>if(reg=syn_code)then //搜索態

state:=sl;

m:=1,

else

m:=0;

end if;

(2)在校核態,其VHDL語言描述如下

if(clk'event and clk='1')then

case state is

when s1=>if(reg=syn_code)then //校核態

m:=m+1;

if(m=max_m)then

state:=s2;

m:=O;

end if;

else

state:=s0;

m:=0;

end if;

(3)在同步態,其VHDL語言描述如下:

if(clk'event and clk='1')then

case state is

when s2=>if(reg=syn_code)then //同步態

n:=0;

else

n:=n+1;

if(n=max_n)then

state:=s0;

n:=Os

end if

end if

3 系統仿真

假定同步碼為110100,幀長為14,前方保護為2幀,后方保護為3幀,輸人數據data為:

010 11010001010100 010 11010001010100 1010001010100 01010101010100 11010001010100 10000001010100 10000001010100 10000001010100 10

則輸出syn的仿真波形如圖2所示。

由圖2可以看出,系統剛開始時處于搜索態,當系統捕獲到同步碼時,即進入校核態;當系統連續2次捕獲到同步碼時,系統進入同步狀態。在同步態,系統只有連續3次丟失幀同步碼時才確認失步,重新進入搜索態。在具體應用中,可根據實際需要對程序中的同步碼、幀長、前后方保護時間進行調整,使系統處于最佳工作狀態。

|

4 結 語

由于VHDL對設計的描述具有相對獨立性,因此設計者可以不懂硬件的結構,只需知道設計的目標。這種設計方法集設計、模擬、綜合為一體的設計方法,能有效地縮短電路設計周期,減少可能發生的錯誤,降低了開發成本,在未來現代數字系統中將會起著越來越重要的作用。用VHDL來進行數字系統設計既方便又簡單,還具有良好的可移植性和維護性,代表著現代數字系統設計的走向。

評論