科研前線 | 更強的線路互連工藝,臺積電SAV技術捷報

直擊前線科研動態

盡在芯片揭秘●科研前線

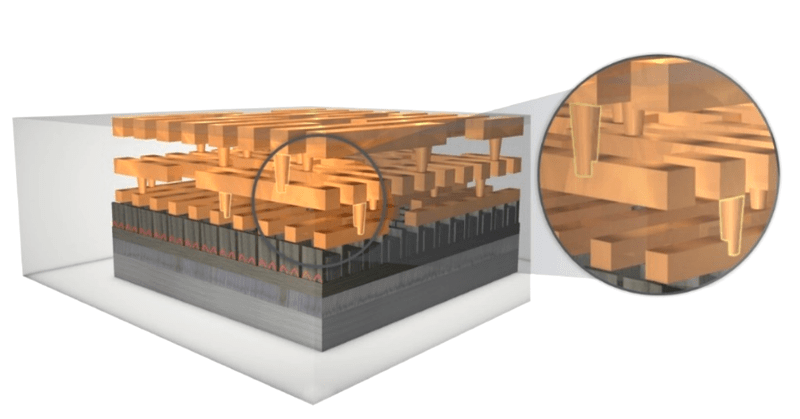

最新一屆IEDM會議論文近日已公開,集成電路制造龍頭臺積電發表了多篇有關先進工藝的研究成果,其自對準通孔SAV工藝,在電特性、器件可靠性和良率方面均有良好表現,將是其保持行業龍頭地位關鍵研究之一。

在先進的節點中,特征尺寸變化和邊緣放置誤差(EPE)*是3nm以下工藝節點中互聯層微縮環節不可避免的工藝難題,它們導致漏電和可靠性。為克服這一挑戰,發展了多種方法來形成SAV自對準通孔,包括金屬線凹進和蝕刻阻擋層的選擇性沉積工藝等。基于SAV的濕法金屬凹陷和阻擋層提出的工藝方案,可以增加孔-線間隙,提高TDDB(經時介電層擊穿)和通孔關鍵尺寸控制。

作為集成電路制造的引領者,臺積電也在布局這一前沿領域,相關成果以Fully Self-Aligned Via Integration for Interconnect Scaling Beyond 3nm Node為題發表于2021年IEEE國際電子器件會議(IEDM),H.P. Chen為第一作者及通訊作者。

*邊緣放置誤差,Edge Placement Error,是光刻軟件仿真出的曝光后光刻膠圖形邊緣與設計圖形之間的差,見下圖圖示。

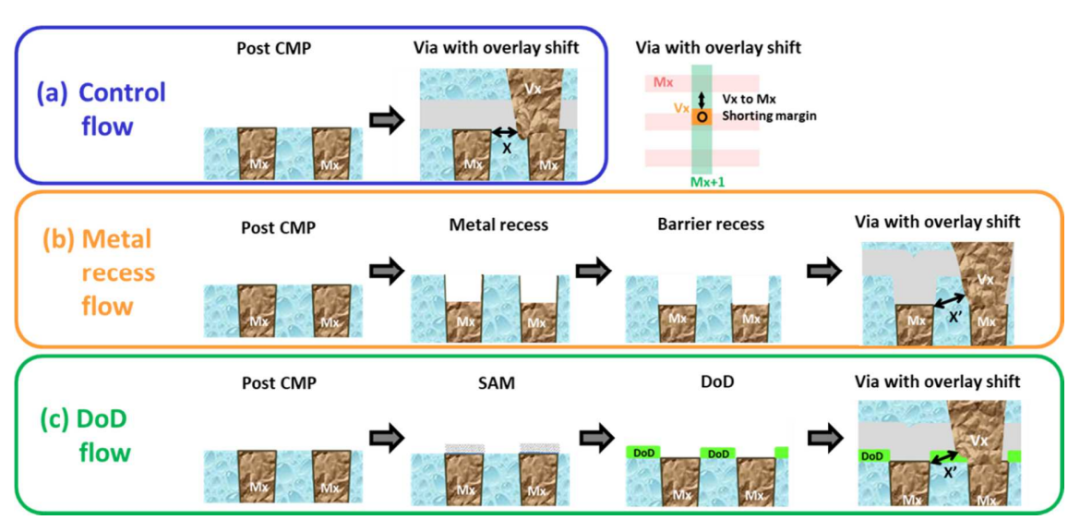

臺積電工藝研發團隊研究兩種方案全自對準通孔SAV工藝,分別通過金屬凹陷法和面積可選擇性電介質上電介質(DoD)實現。其主要研究內容包括:

發現布線流程中更大對角距對于自對準工藝的重要影響;

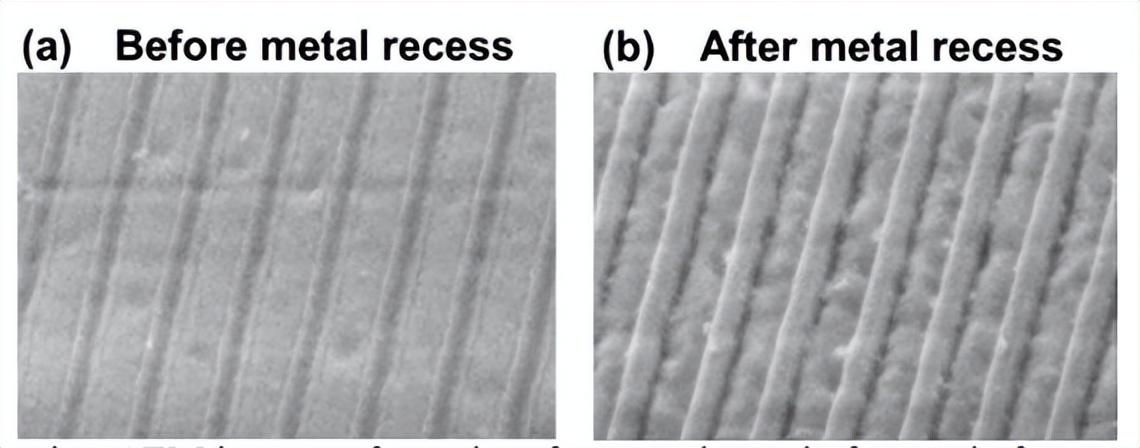

金屬凹陷工藝存在均勻性差、表面粗糙度高、金屬完整性(metal integrity)衰減等問題;

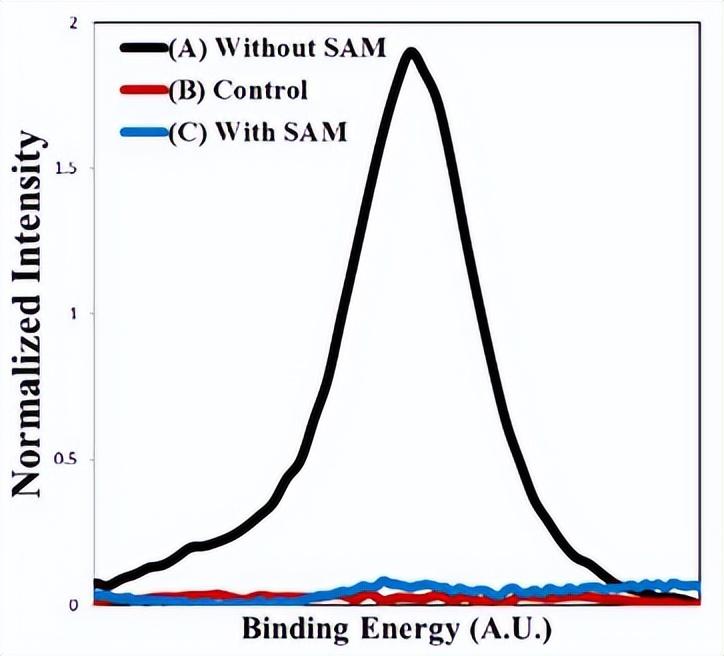

DoD工藝通過采用選擇性自組裝單層阻擋材料,實現了向上越階電介質沉積的工藝,并展示出高達兩個數量級的經時介電層擊穿的改善;

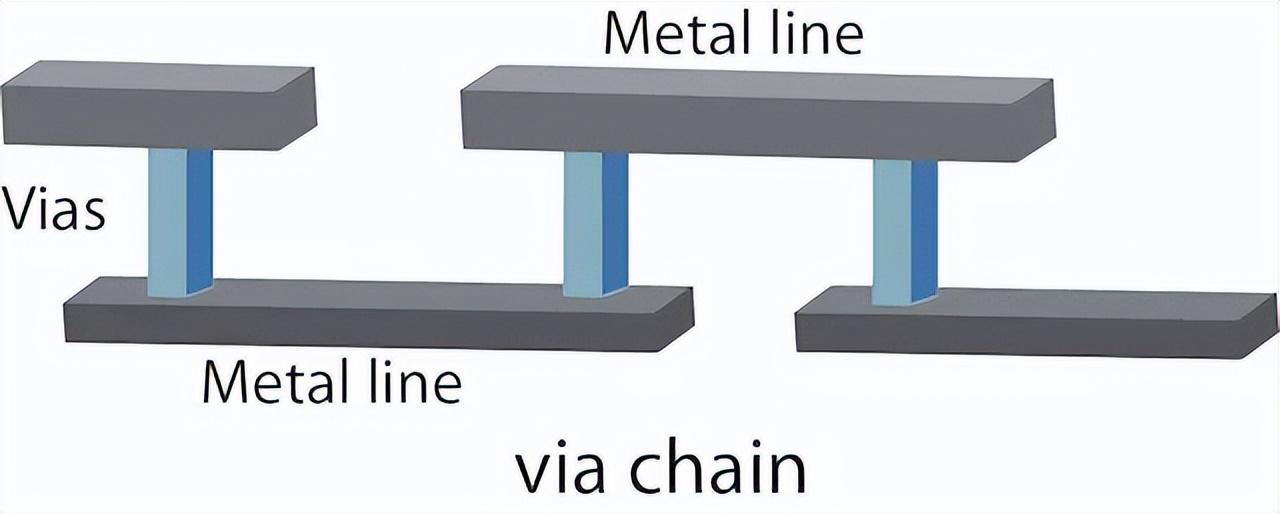

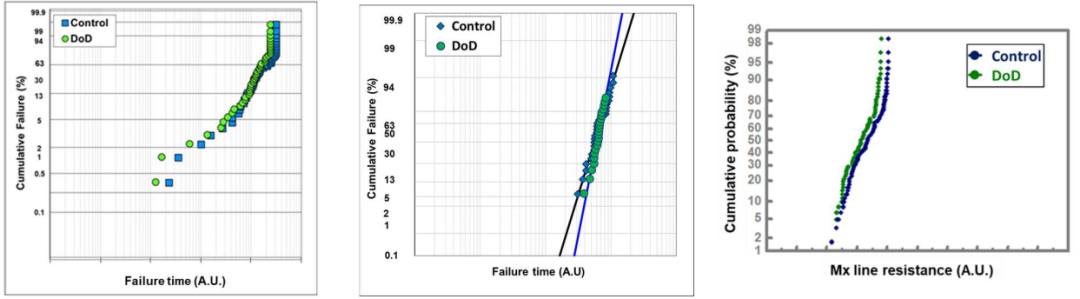

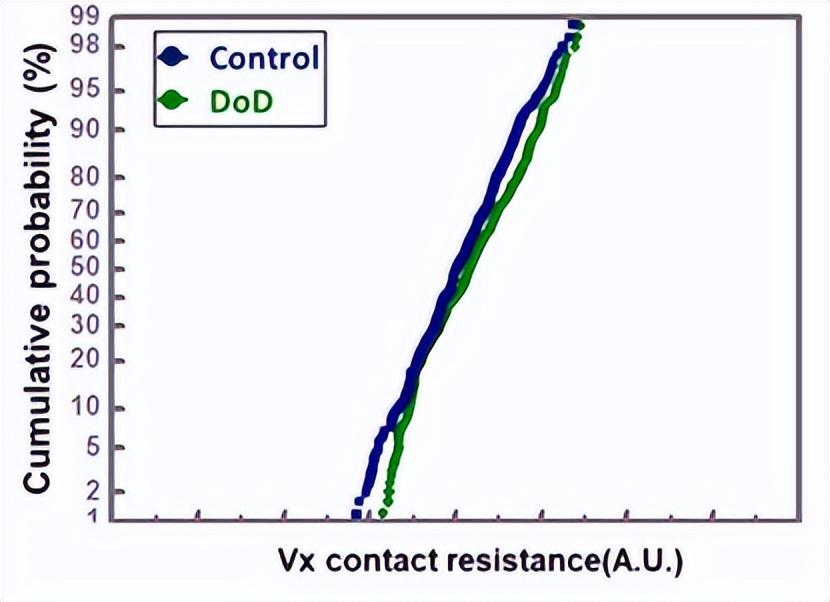

對DoD工藝在孔-線電阻、via-chain(見下圖)良率、金屬線TDDB和EM可靠性的表現進行測試,達到了量產水平。

via-chain結構示意圖 (圖源:techdesign)

工藝流程示意圖

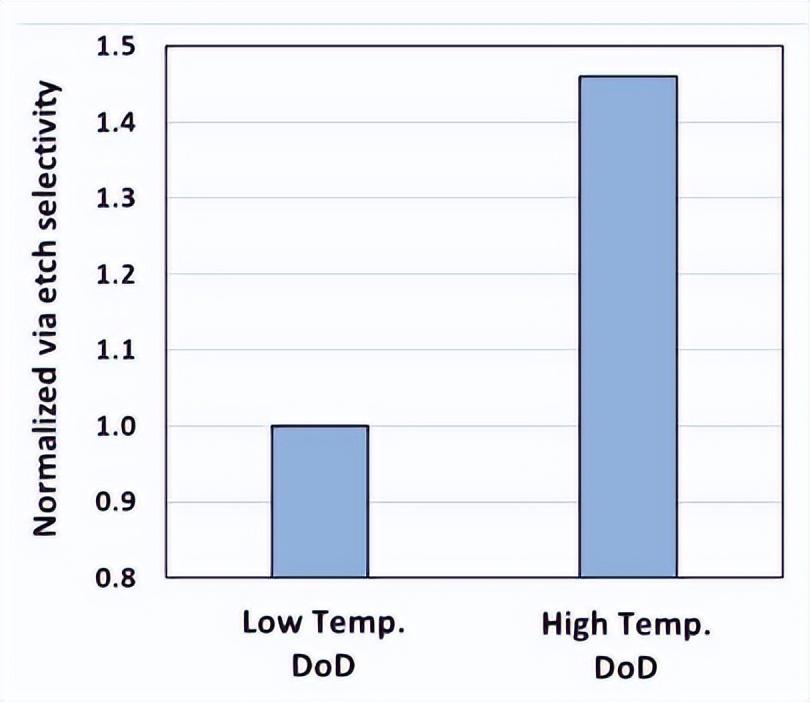

高低溫下的通孔刻蝕可選擇性對比

金屬表面粗糙度SEM形貌像對比

DoD信號在三種沉積方法下的X射線能譜

金屬線間TDDB壽命(左)、EM壽命(中) 以及金屬線電阻(右)

通孔接觸電阻變化曲線

研究團隊通過評估2.5、D封裝、兩種FOCoS封裝這三種異質集成封裝的力學性能和熱性能,驗證了有限元模型的有效性,并且通過比較發現FOCoS相比2.5D封裝具有更好的電氣性能與熱性能,在熱膨脹錯配和散熱方面表現良好,日月光也對該技術替代硅中介層解決方案的寄予厚望,相信未來能在豐富的應用領域占有一席之地。

臺積電研究團隊實現了可應用于亞3nm工藝的線路互連微縮,具有低金屬線電阻、通孔電阻和高良率的優勢,可預見將在未來進一步助力臺積電3nm、2nm工藝的成熟落地,為其集成電路制造龍頭地位保駕護航。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。