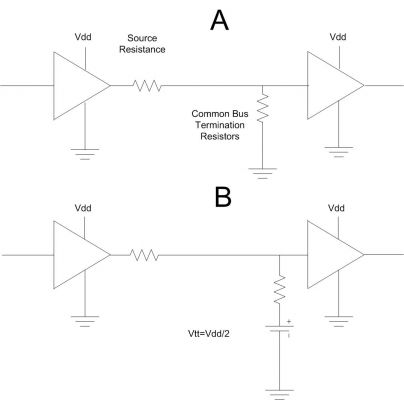

1. 定義DDR:Double Date Rate 雙倍速率同步動態隨機存儲器。DDR、DDR2、DDR3常用規格:2. 阻抗控制要求單端走線控制 50 歐姆,差分走線控制 100 歐姆3. DDR 布局要求通常,根據器件的擺放方式不同而選擇相應的拓撲結構。A、DDR*1 片,一般采用點對點的布局方式,靠近主控,相對飛線 Bank 對稱。間距可以按照是實際要求進行調整,推薦間距為 500-800mil。B、DDR*2 片,布局相對主控飛線 Bank 對稱,常采用 T 型拓撲結構, 推薦間距如下:等長要求

關鍵字:

DDR PCB設計 存儲

1、電源DDR的分類A、主電源VDD和VDDQ主電源的要求是VDDQ=VDD,VDDQ是給IO buffer供電的電源,VDD是給內核供電。但是一般的使用中都是把VDDQ和VDD合成一個電源使用。有的芯片還有專門的VDDL,是給DLL供電的,也和VDD使用同一電源即可。電源設計時,需要考慮電壓、電流是否滿足要求。電源的上電順序和電源的上電時間,單調性等。電源電壓的要求一般在±5%以內。電流需要根據使用的不同芯片,及芯片個數等進行計算。由于DDR的電流一般都比較大,所以PCB設計時,如果有一個完整的電源平面

關鍵字:

電源設計 DDR

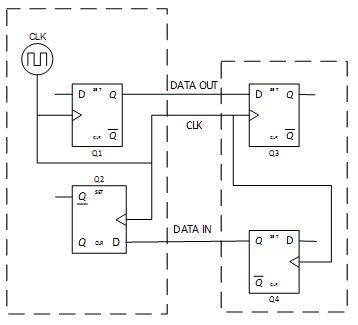

了解雙數據速率(DDR)存儲器的關鍵概念和圍繞這一數字通信技術的應用,其中兩個數據字在一個時鐘周期內傳輸。串行數據傳輸比并行數據傳輸具有重要優勢,并且在許多系統中,這些優勢足夠顯著,足以證明添加串行化和反串行化并行數據的電路是合理的,從而可以將其作為串行數據傳輸。然而,計算機存儲器是并行數據傳輸仍然普遍存在的一個應用領域。由于它們可以同時讀取和寫入許多數字信號,并行接口速度很快,設計師們一直在尋找使其更快的方法。一種用于實現數據傳輸速率的大幅提高的古老但仍然相關的技術被稱為雙泵浦,而這一特性正是將存儲器系

關鍵字:

雙倍數據速率,DDR

近日,存儲大廠美光科技在GTC 2024活動,展示一系列存儲解決方案。該公司此前剛宣布8層堆疊HBM3E已量產,并預計2024年第二季搭配NVIDIA H200 GPU出貨。美光展示的解決方案,分別包括8層堆疊24GB HBM3E解決方案與后續12層36GB HBM3E解決方案;使用單片晶粒具低延遲與低功耗優勢的DDR5 RDIMM;支持NVIDIA Grace CPU的LPDDR5X存儲解決方案與LPCAMM2模組;可提供AI與存儲器工作負載所需的容量、頻寬、彈性的CXL存儲器模組,并攜手MemVerg

關鍵字:

DDR 美光科技 HBM

邁過2023年的經濟逆風行業下行周期,2024年存儲市場起勢,存儲芯片價格上漲。為了適配近兩年人工智能熱浪需求,存儲新技術革新步伐加速,DDR、LPDDR、GDDR新技術在2024年迎來放量周期;HBM加速邁進,HBM3/HBM3e持續突破,有望帶動存儲市場迸發新的活力。一2024是DRAM技術迸發活力的一年從1998年三星生產出最早的商用DDR

SDRAM芯片,到DDR1、DDR2、DDR3、DDR4的延續,再到今年躍升主流的DDR5,和即將到來的DDR6、DDR7,DRAM技術還在持續突破。按照不

關鍵字:

存儲 DDR HBM

邁過2023年的經濟逆風行業下行周期,2024年存儲市場起勢,存儲芯片價格上漲。為了適配近兩年人工智能熱浪需求,存儲新技術革新步伐加速,DDR、LPDDR、GDDR新技術在2024年迎來放量周期;HBM加速邁進,HBM3/HBM3e持續突破,有望帶動存儲市場迸發新的活力。一2024是DRAM技術迸發活力的一年從1998年三星生產出最早的商用DDR SDRAM芯片,到DDR1、DDR2、DDR3、DDR4的延續,再到今年躍升主流的DDR5,和即將到來的DDR6、DDR7,DRAM技術還在持續突破。按照不同的

關鍵字:

DDR GDDR6 HBM

1. 電源 DDR的電源可以分為三類:a主電源VDD和VDDQ,主電源的要求是VDDQ=VDD,VDDQ是給IO buffer供電的電源,VDD是給但是一般的使用中都是把VDDQ和VDD合成一個電源使用。有的芯片還有VDDL,是給DLL供電的,也和VDD使用同一電源即可。電源設計時,需要考慮電壓,電流是否滿足要求,電源的上電順序和電源的上電時間,單調性等。電源電壓的要求一般在±5%以內。電流需要根據使用的不同芯片,及芯片個數等進行計算。由于DDR的電流一般都比較大,所以PCB設計時,如果有一個完整的電源平

關鍵字:

DDR 內存

在2024年即將到來之際,多家機構給出預測,認定生成式AI將成為2024年的增長重點之一。回顧2023年,年初的ChatGPT引爆了今年的生成式AI熱潮,不僅僅是下游市場的AI應用,這股大火一直燒到了上游芯片領域,根據權威機構預測,2023年和2024年,AI服務器將有38%左右的增長空間。隨著GPU等AI芯片走向高峰的同時,也極大帶動了市場對新一代內存芯片HBM(高帶寬內存)的需求。 HBM是何方神圣? 首先,我們先來了解一下什么是HBM。HBM全稱為High Bandwich Me

關鍵字:

HBM DDR AI GPU 美光 海力士

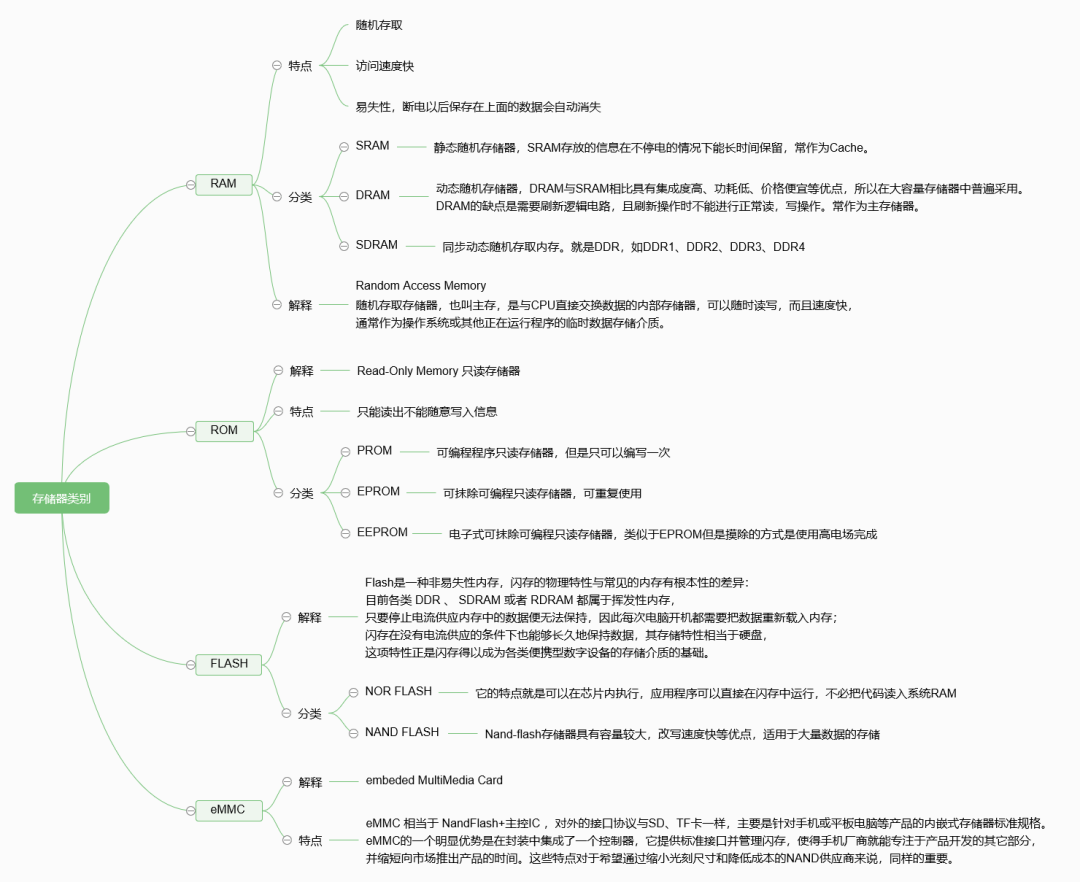

簡單解釋ROMROM:只讀存儲器,內容寫入后就不能更改了,制造成本比較低,常用于電腦中的開機啟動如啟動光盤bios,在系統裝好的電腦上時,計算機將C盤目錄下的操作系統文件讀取至內存,然后通過cpu調用各種配件進行工作這時系統存放存儲器為RAM。PROM:可編程程序只讀存儲器,但是只可以編寫一次。EPROM:可抹除可編程只讀存儲器,可重復使用。EEPROM:電子式可抹除可編程只讀存儲器,類似于EPROM但是摸除的方式是使用高電場完成。RAMRAM:隨機存取存儲器,也叫主存,是與CPU直接交換數據的內部存儲器

關鍵字:

ROM RAM FLASH DDR EMMC

一站式定制芯片及IP供應商——燦芯半導體日前宣布推出用于高速DDR物理層中的Zero-Latency (零延遲)和True-Adaptive(真自適應)兩項技術。這兩項技術已經開始在12/14 FinFET, 22/28nm的DDR4/LPDDR4,4x高性能物理層IP上進行部署,將為客戶帶來更高效、更穩定的全新體驗。 Zero-Latency (零延遲) 技術在讀數據通路上,采用了兩種可選的、獨特的采樣方式進行數據轉換,而不像其他DDR物理層供貨商采用FIFO進行跨時鐘域轉換,此技術將延遲降低

關鍵字:

燦芯 DDR IP

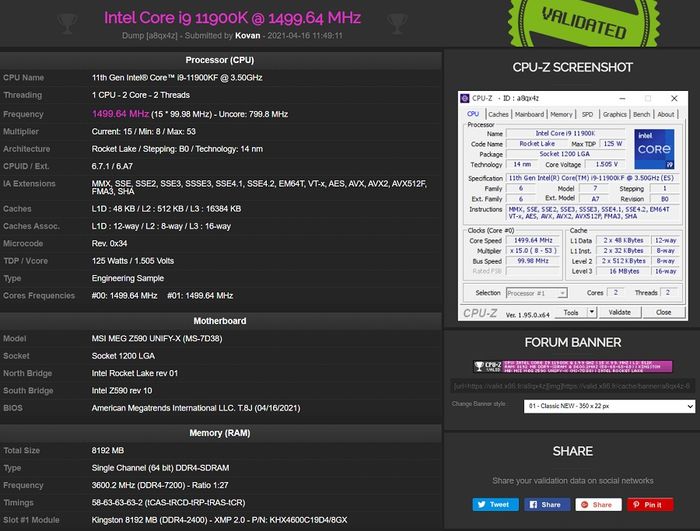

DDR4內存已經誕生了有10年之久,從一開始的2133MHz頻率到后期逐漸站上2400MHz、2666MHz,一直到工藝與電路架構升級后,現在民用普遍的3200MHz和性能玩家追捧的4166MHz。可以說這十年以來,DDR4內存的頻率也是有了快翻倍的提升。 而日前,有超頻愛好者將DDR4內存的頻率超頻至7200MHz,打破了世界紀錄。該記錄由微星MEG Z590 Unify-X主板創造,超頻內存上使用了兩條士頓的HyperX Predator 8GB內存,組成16GB雙通道。為了能讓內存實現如此高頻

關鍵字:

DDR

要點: 用于GF 12LP+解決方案的DesignWare IP核產品組合包括USB4、PCIe 5.0、Die-to-Die HBI和112G USR/XSR、112G Ethernet、DDR5、LPDDR5、MIPI、OTP NVM等 兩家公司之間的長期合作已成功實現了DesignWare IP核從180納米到12納米的開發,可應用于廣泛領域新思科技(Synopsys, Inc.,納斯達克股票代碼:SNPS)今日宣布與GLOBALFOUNDRIES?(GF?)開展合作,開發用于G

關鍵字:

新思科技 12LP+FinFET DesignWare IP

重點:高質量DesignWare DDR PHY IP核為NVIDIA提供無與倫比的性能、延遲和電源效率DDR PHY支持DDR5/4的每個通道多個DIMM,滿足NVIDIA的網絡數據速率和內存容量要求基于固件的現場可升級訓練可提高通道的穩定性和可靠性,并且有助于算法更新,從而降低采用新內存協議的風險新思科技(Synopsys, Inc.)近日宣布,NVIDIA的網絡業務部門Mellanox將采用經驗證的DesignWare? DDR5/4 PHY IP核,以滿足其針對高性能計算和人工智能應用的Infin

關鍵字:

云計算 NVIDIA 新思科技 DesignWare DDR IP核

新思科技宣布,Graphcore采用新思科技基于Verdi?調試的VCS?仿真解決方案,驗證其最近推出Colossus? GC200智能處理單元(IPU),該產品足以改變行業游戲規則。Graphcore的第二代IPU是有史以來最復雜的微處理器,擁用594億個晶體管和1472個獨立處理器內核。新思科技VCS讓Graphcore能夠為其大規模平行IPU設計,特別針對機器智能(machine

intelligence)工作負載,顯著提高仿真吞吐量。Graphcore芯片業務副總裁Phi

關鍵字:

Tenstorrent 新思科技 DesignWare IP AI

重點:Tenstorrent采用DesignWare PCI Express 4.0、ARC HS48處理器和LPDDR4 IP,一次性完成其Graysull 人工智能(AI)處理器芯片的硅晶設計PCI Express 4.0控制器與PHY IP達到最高x16鏈接寬度,可處理超過36dB的信道損耗,提供低延遲和高吞吐量連接采用超標量架構的四核ARC HS48處理器IP提供卓越的節能性能和可擴展性低延遲LPDDR4控制器IP提供內存電源狀態的自動優化,以實現低功耗以及高可靠性的高級RAS功能新思科技(Syn

關鍵字:

Tenstorrent 新思科技 DesignWare IP AI

designware ddr介紹

您好,目前還沒有人創建詞條designware ddr!

歡迎您創建該詞條,闡述對designware ddr的理解,并與今后在此搜索designware ddr的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473