引言:DDR4 等存儲技術的發展帶動存儲器速度與功率效率空前提升,僅僅停留在一致性測試階段,已經不能滿足日益深入的調試和評估需求。DDR 存儲器的測試項目涵蓋了電氣特性和時序關系,由JEDEC明確定義,JEDEC 規范并

關鍵字:

高速存儲器 一致性測試 DDR

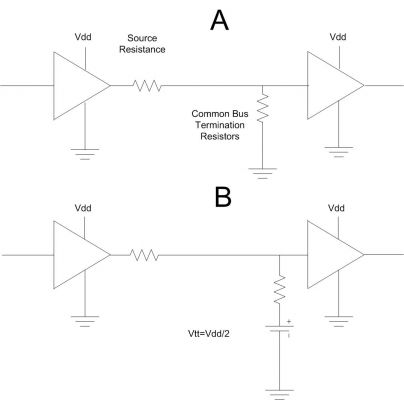

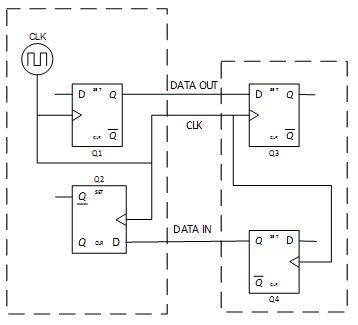

高速電路設計領域,關于布線有一種幾乎是公理的認識,即“等長”走線,認為走線只要等長就一定滿足時序需求,就不會存在時序問題。本文對常用高速器件的互連時序建立模型,并給出一般性的時序分析公式。為

關鍵字:

PCB DDR SDRAM PHY芯片

SDRAM與DDR SDRAM

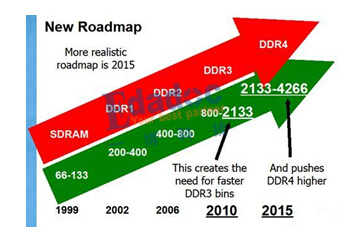

SDRAM是比較久遠的事情了,但我們一說到它肯定不會和 DDR混淆,我們通常理解的SDRAM其實是SDR SDRAM,為SDRAM的第一代,而DDR1則為第二代,乃至到我們現在使用的DDR4,其實為第五代SDRAM,在此需要澄清一下。以示區別,后續文 章里面用SDR來特指SDR SDRAM,而DDR就特指DDR SDRAM了。

就像很多人回復的一樣,他們的本質區別就是周期操作方 式(也稱時鐘采樣)的差異,這就導致后面設計上很大的不同。SDR都是“

關鍵字:

DDR SDRAM

混合信號半導體解決方案供應商 IDT® 公司宣布支持基于 Nehalem 的 Intel® Xeon® 處理器,該處理器采用可進行生產的 PCI Express®(PCIe®)交換和計

關鍵字:

IDT DDR

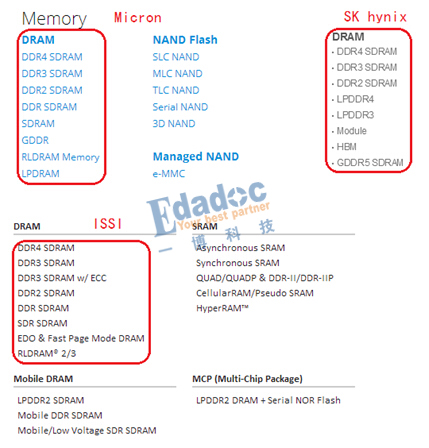

射頻功率、成像和高可靠性半導體解決方案領域的領軍企業 e2v aerospace and defense, Inc. (e2v ad) 近日宣布,將延長世界領先高級存儲解決方案供應商之一 Mic

關鍵字:

Micron e2v DDR

DDR SDRAM全稱為Double Data Rate SDRAM,中文名為“雙倍數據率SDRAM”。DDR是在原有的SDRAM的基礎上改進而來,嚴格的說DDR應該叫DDR SDRAM,人們習慣稱為DDR。

說到這里,很多人可能會問SDRAM、DRAM、SRAM或者RAM、ROM到底是什么鬼,怎么區別的?小編還是來簡單普及下關于存儲的基礎知識吧。

ROM 和RAM指的都是半導體存儲器,ROM是只讀存儲器(Read-Only Memory)的簡稱,是一種只能讀出事先

關鍵字:

DDR DRAM

新思科技(Synopsys, Inc.)日前宣布:推出全新的DesignWare? USB-C 3.1/DisplayPort 1.3知識產權(IP)解決方案,該解決方案集成了USB Type-C?(USB-C?)、SuperSpeed USB 10 Gbps(USB 3.1 Gen 2)和DisplayPort 1.3接口,以及帶有高帶寬數字內容保護(HDCP)2.2 I

關鍵字:

Synopsys DesignWare

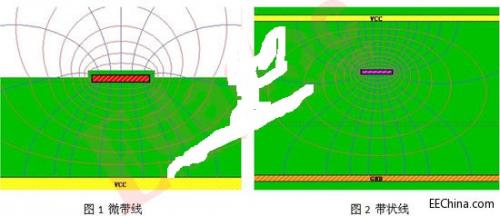

信號在媒質中傳播時,其傳播速度受信號載體以及周圍媒質屬性決定。在PCB(印刷電路板)中信號的傳輸速度就與板材DK(介電常數),信號模式,信號線與信號線間耦合以及繞線方式等有關。隨著PCB走線信號速率越來越高,對時序要求較高的源同步信號的時序裕量越來越少,因此在PCB設計階段準確知道PCB走線對信號時延的影響變的尤為重要。本文基于仿真分析DK,串擾,過孔,蛇形繞線等因素對信號時延的影響。

1.引言

信號要能正常工作都必須滿足一定的時序要求,隨著信號速率升高,數字信號的發展經歷了從共同步時鐘到

關鍵字:

PCB DDR

是德科技公司日前在 DesignCon 2015 展會上展示其高速數字解決方案。本屆展會于 1 月 28 日到 29 日在美國加州圣克拉拉會展中心舉行,是德科技展位設于第 725 號展臺。是德科技非常自豪能夠接替其前身惠普公司和安捷倫公司,繼續擔任 DesignCon 展會的發起方和主辦方。一年一度的 DesignCon 展會即將迎來其 20 周年紀念日。作為主要面向高速通信和半導體行業中的芯片、電路板和系統設計工程師的一項活動,它已成為行業中最重要的展會。

是德科技將展出眾多仿真、建模、測試和

關鍵字:

是德科技 DDR

Memory是系統運行和性能的核心。設計人員需要更好地了解內存子系統,以優化系統吞吐能力。

如今Memory炙手可熱。最近在加利福尼亞州舉行的2014 MemCon盛況空前,展廳里展示了幾乎所有關于Memory的產品,參會的人也熱情高漲。

會議主題是,是否有更為行之有效的方法來特性化分析DDR Memory的系統裕量。尤其是DDR子系統(DDR controller, PHY和 I/O))被嵌入到芯片用于承擔處理器和外部DDR存儲器之間的數據交互任務,這使得這種分析變得更加困難。 要知道,

關鍵字:

MEMCON Memory DDR-SDRAM

彈性客制化IC設計領導廠商(Flexible ASIC Leader™)創意電子(Global Unichip Corp.,GUC)與高度創新的fabless Soc – centric IC芯片設計公司, 信驊科技(ASPEED Technology, Inc.)采用業界第一個以臺積電公司40nm低功耗(Low Power,LP)工藝節點的DDR3/4 PHY,大幅加速了一遠程管理控制器的系統設計, 此控制器用于服務器及桌面虛擬化。

創意電子的DDR 3/4 PHY為業

關鍵字:

創意電子 ASIC DDR

加速芯片和電子系統創新而提供軟件、知識產權(IP)及服務的全球性領先供應商新思科技公司(Synopsys, Inc.,納斯達克股票市場代碼:SNPS)日前宣布:其用于高壓工藝的DesignWare AEON Trim NVM IP開始供貨。與其它的NVM IP解決方案相比,該款全新的IP將面積縮小達75%,同時有助于降低汽車IC的成本和尺寸。該IP可用于標準的180納米5V CMOS和BCD工藝,而不需要額外的光罩或工藝步驟。DesignWare NVM IP支持Grade 0汽車應用所需要的寬溫度范圍,

關鍵字:

Synopsys DesignWare AEC-Q100

新思科技公司(Synopsys, Inc)日前宣布:其多協議DesignWare? Enterprise 12G PHY IP正式上市,該物理層知識產權(PHY IP)將使多樣化的高端網絡和計算應用在功耗降低的同時提升了性能。DesignWare Enterprise 12G PHY是專門為應對設計師們所面臨的不斷增長的性能/功耗平衡挑戰而設計,它使設計師能夠輕松地將各種企業級通信協議集成到他們的系統級芯片(SoC)上,包括PCI Express 3.0、SATA 6G、10GBASE-KR、10GB

關鍵字:

Synopsys DesignWare

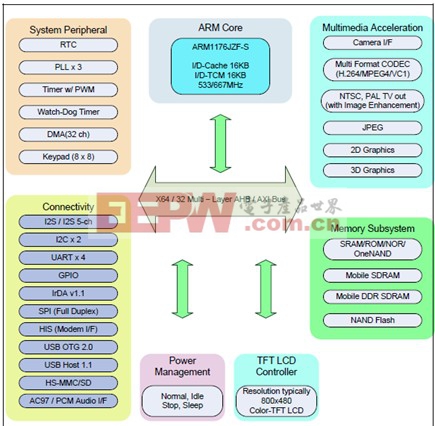

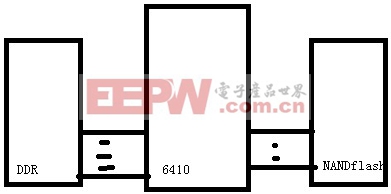

當在S3C6410跑操作系統的時候,我們不太會注意S3C6410的內存使用情況,但是,當我們做裸板測試時,該處理器的8K的片內內存的使用就不得不注意,一旦編寫的程序大小超過了片內內存的大小,我們就不能得到正確的結果,究其原因,我們先看一下S3C6410的啟動過程。

關鍵字:

ARM11 DDR NANDflash 內存

designware ddr介紹

您好,目前還沒有人創建詞條designware ddr!

歡迎您創建該詞條,闡述對designware ddr的理解,并與今后在此搜索designware ddr的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473