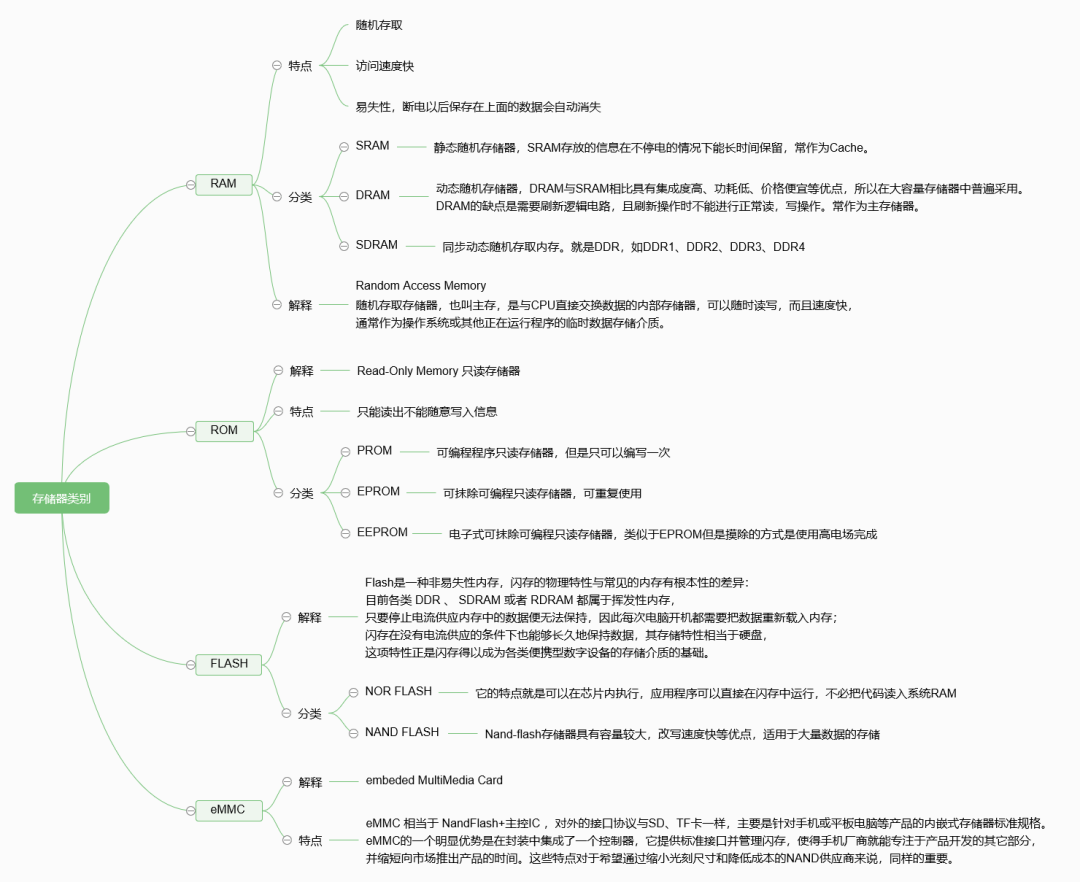

雙倍數(shù)據(jù)速率(DDR)內(nèi)存簡(jiǎn)介

了解雙數(shù)據(jù)速率(DDR)存儲(chǔ)器的關(guān)鍵概念和圍繞這一數(shù)字通信技術(shù)的應(yīng)用,其中兩個(gè)數(shù)據(jù)字在一個(gè)時(shí)鐘周期內(nèi)傳輸。

本文引用地址:http://www.104case.com/article/202405/458877.htm串行數(shù)據(jù)傳輸比并行數(shù)據(jù)傳輸具有重要優(yōu)勢(shì),并且在許多系統(tǒng)中,這些優(yōu)勢(shì)足夠顯著,足以證明添加串行化和反串行化并行數(shù)據(jù)的電路是合理的,從而可以將其作為串行數(shù)據(jù)傳輸。然而,計(jì)算機(jī)存儲(chǔ)器是并行數(shù)據(jù)傳輸仍然普遍存在的一個(gè)應(yīng)用領(lǐng)域。由于它們可以同時(shí)讀取和寫(xiě)入許多數(shù)字信號(hào),并行接口速度很快,設(shè)計(jì)師們一直在尋找使其更快的方法。

一種用于實(shí)現(xiàn)數(shù)據(jù)傳輸速率的大幅提高的古老但仍然相關(guān)的技術(shù)被稱(chēng)為雙泵浦,而這一特性正是將存儲(chǔ)器系統(tǒng)轉(zhuǎn)變?yōu)殡p數(shù)據(jù)速率(DDR)存儲(chǔ)器系統(tǒng)的原因。“單泵”存儲(chǔ)系統(tǒng)采用了歷史悠久的策略,將數(shù)據(jù)從一個(gè)IC同步移動(dòng)到另一個(gè)IC。基本上,邏輯信號(hào)每時(shí)鐘周期改變一次,并且由接收器在時(shí)鐘的上升沿或下降沿上采樣。在這個(gè)方案中,字被傳輸?shù)乃俾什荒艹^(guò)時(shí)鐘頻率。

例如,如果您的時(shí)鐘運(yùn)行在133 MHz,則(理想情況下)每秒可以傳輸1.33億個(gè)單詞。請(qǐng)注意,比特傳輸速率取決于系統(tǒng)架構(gòu),因?yàn)椴煌挠?jì)算系統(tǒng)使用不同的字長(zhǎng)——8比特、16比特等。雙泵浦系統(tǒng)可以在133 MHz時(shí)鐘下實(shí)現(xiàn)266 MT/s(每秒數(shù)百萬(wàn)次傳輸)。

在本文中,我們將了解單數(shù)據(jù)速率接口和雙數(shù)據(jù)速率接口之間的差異,我們使用DDR的原因及其應(yīng)用程序。

SDR與DDR:?jiǎn)螖?shù)據(jù)速率和雙數(shù)據(jù)速率接口

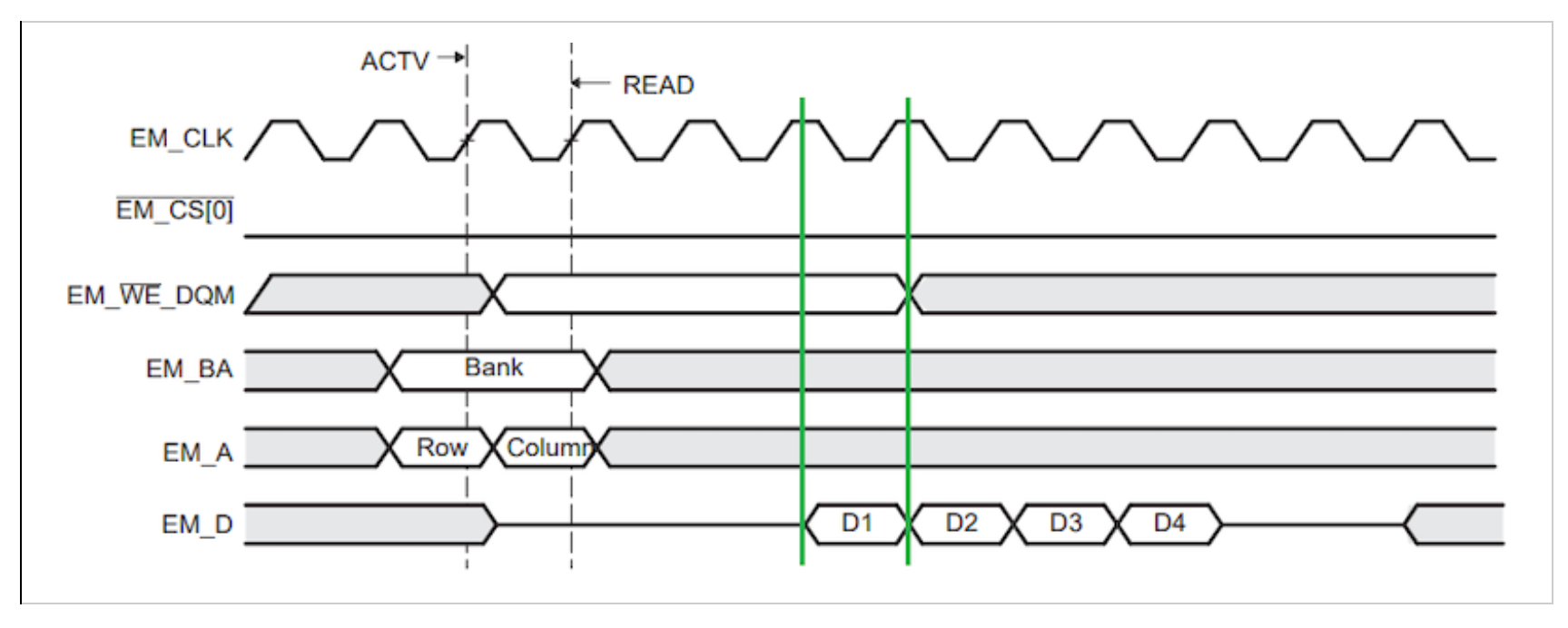

下圖1所示的時(shí)序圖是單個(gè)數(shù)據(jù)速率存儲(chǔ)器接口的一個(gè)示例。

單個(gè)數(shù)據(jù)速率存儲(chǔ)器接口的示例。

圖1。單個(gè)數(shù)據(jù)速率存儲(chǔ)器接口的示例。圖片[修改]由德州儀器提供

首先,使用EM_BA信號(hào)來(lái)選擇存儲(chǔ)器組,并且通過(guò)EM_A信號(hào)來(lái)建立行地址和列地址。在EM_D引腳上輸出數(shù)據(jù)字D1、D2、D3和D4。注意一個(gè)數(shù)據(jù)字如何占據(jù)EM_CLK信號(hào)的整個(gè)周期。

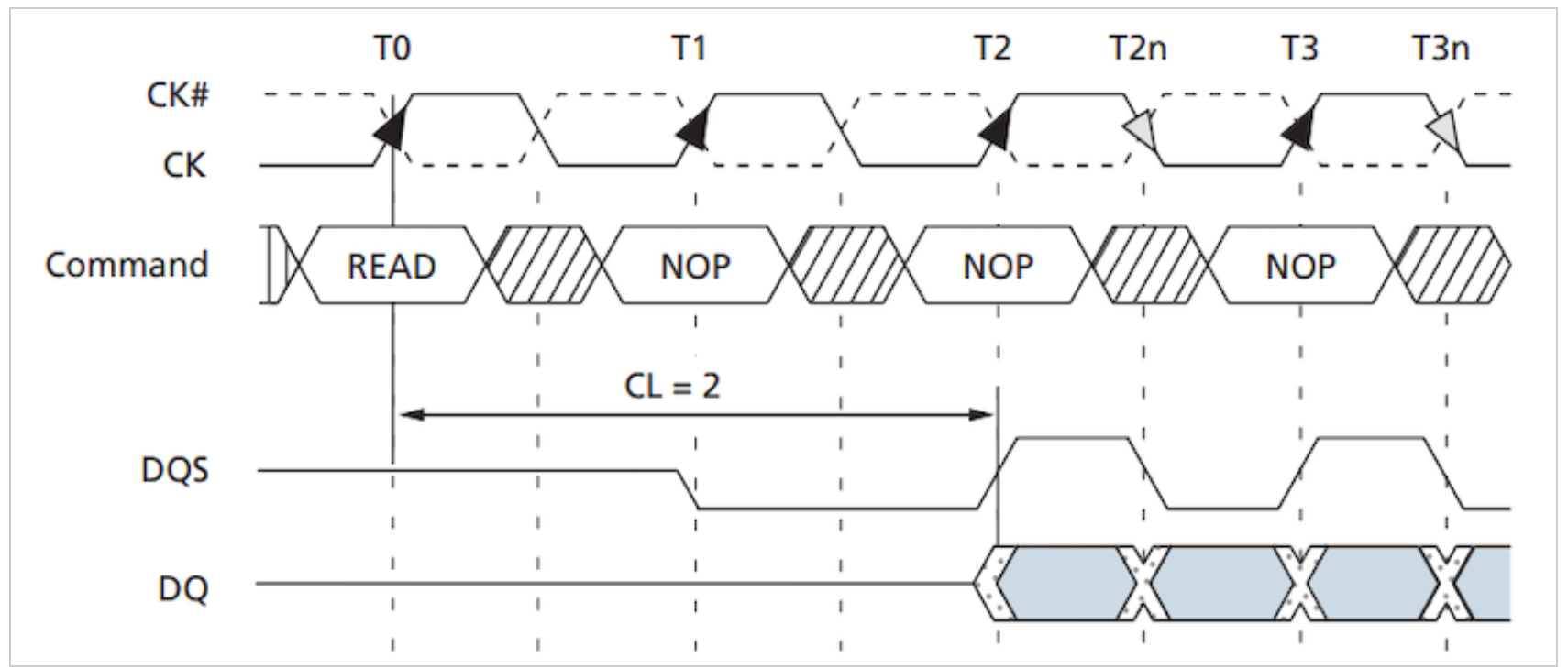

我們將看到的下一個(gè)時(shí)序圖(圖2)描述了一個(gè)雙數(shù)據(jù)速率接口。

雙數(shù)據(jù)速率接口的示例。

圖2:雙數(shù)據(jù)速率接口的示例。圖片由美光提供

“DQ”線表示數(shù)據(jù)信號(hào),陰影區(qū)域之間的未陰影X形區(qū)域表示從一個(gè)字到下一個(gè)字的轉(zhuǎn)換。你可以看到,每個(gè)單詞只需要半個(gè)完整的時(shí)鐘周期。請(qǐng)記住,此芯片使用差分時(shí)鐘,這就是時(shí)序圖具有CK信號(hào)和互補(bǔ)CK#信號(hào)的原因。

動(dòng)機(jī):為什么數(shù)據(jù)速率加倍?

你可能會(huì)想,當(dāng)工程師們本可以將時(shí)鐘頻率提高兩倍時(shí),他們?yōu)槭裁匆闊┑貫镈DR信號(hào)創(chuàng)建新的邏輯。這一決定的主要解釋包含在兩個(gè)詞中,這兩個(gè)詞代表了無(wú)數(shù)小時(shí)的高速研發(fā):信號(hào)完整性。

高頻信號(hào)——相對(duì)于給定技術(shù)時(shí)代或應(yīng)用場(chǎng)景的限制來(lái)理解“高頻”——是電路板設(shè)計(jì)師非常震驚的來(lái)源。這些信號(hào):

由于信道帶寬有限而導(dǎo)致更多色散

需要更多的功耗

更容易受到電容耦合和反射的影響,

從任何PCB上的各種非故意天線更有效地輻射

使用測(cè)試設(shè)備對(duì)它們進(jìn)行表征和故障排除也更加困難。例如,示波器的模擬和數(shù)字帶寬有限,隨著頻率的增加,它會(huì)在波形中引入更多失真。

因此,在嘗試實(shí)現(xiàn)更高的時(shí)鐘速率之前,從現(xiàn)有時(shí)鐘速率中提取盡可能多的吞吐量是有意義的。通過(guò)從單個(gè)數(shù)據(jù)速率接口轉(zhuǎn)移到DDR接口,設(shè)計(jì)者可以在不改變系統(tǒng)最大信號(hào)頻率的情況下顯著提高數(shù)據(jù)傳輸速率。所有這一切都可以實(shí)現(xiàn),即使數(shù)據(jù)信號(hào)的最大頻率已經(jīng)增加了2倍——這個(gè)新的數(shù)據(jù)頻率不高于先前的時(shí)鐘頻率。

DDR內(nèi)存應(yīng)用程序

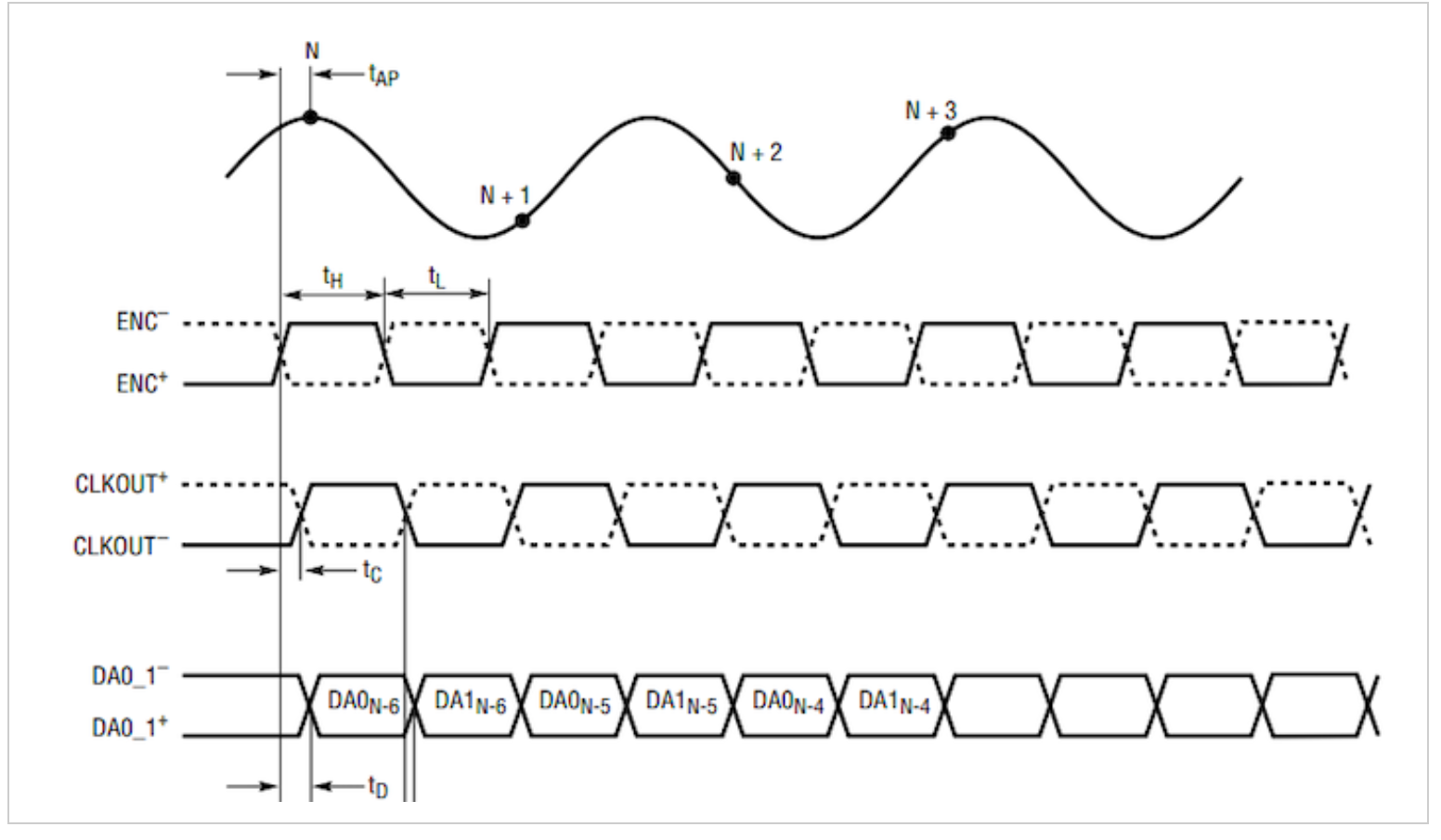

雙泵浦是一種通用功能,已在各種并行數(shù)據(jù)傳輸接口中使用。甚至高速數(shù)據(jù)轉(zhuǎn)換器也采用了這種技術(shù)。例如,在圖3所示的模數(shù)轉(zhuǎn)換器(ADC)時(shí)序圖中,一個(gè)樣本在一個(gè)完整時(shí)鐘周期所需的時(shí)間內(nèi)被數(shù)字化,但數(shù)字輸出使用DDR時(shí)序,因?yàn)閮蓚€(gè)數(shù)據(jù)位被復(fù)用到每個(gè)輸出上。

示例ADC時(shí)序圖,其中所示的所有信號(hào)都是差分信號(hào)。

圖3。示例ADC時(shí)序圖,其中所示的所有信號(hào)都是差分信號(hào)。模擬/線性技術(shù)提供的圖像

然而,DDR并行傳輸仍然與計(jì)算系統(tǒng)中使用的SDRAM(同步動(dòng)態(tài)隨機(jī)存取存儲(chǔ)器)密切相關(guān)。幾十年來(lái),工程師們一直在努力提高計(jì)算機(jī)移動(dòng)和處理數(shù)字?jǐn)?shù)據(jù)的速度,DDR信號(hào)使他們的吞吐量翻倍,同時(shí)保持當(dāng)時(shí)可行的最大時(shí)鐘頻率。

1998年發(fā)布的第一代DDR SDRAM支持高達(dá)200 MHz的時(shí)鐘頻率和高達(dá)400 MT/s的相應(yīng)傳輸速率。然后是DDR2、DDR3、DDR4,最后是我們目前使用的DDR5。DDR5的最大傳輸速率超過(guò)7 GT/s。

評(píng)論