cpu ip 文章 最新資訊

全新Arm IP Explorer平臺(tái)助力SoC架構(gòu)師與設(shè)計(jì)廠商加速IP選擇

- Arm 推出全新 Arm IP Explorer 平臺(tái),該平臺(tái)是一套由 Arm 提供的云平臺(tái)服務(wù),旨在為基于 Arm 架構(gòu)設(shè)計(jì)系統(tǒng)的硬件工程師與 SoC 架構(gòu)師,加速其 IP 選擇和 SoC 設(shè)計(jì),為 IP 選擇流程帶來躍階式的效率提升,進(jìn)而有效提高其開發(fā)和生產(chǎn)效率。為了加快產(chǎn)品推向市場(chǎng),搶占商機(jī),能在 SoC 設(shè)計(jì)流程的任一環(huán)節(jié)中提速都至關(guān)重要。Arm全新推出的 Arm IP Explorer 在針對(duì)用戶選擇 IP 的痛點(diǎn)進(jìn)行流程優(yōu)化,通過探索、設(shè)計(jì)和分享三方面的多樣功能達(dá)到效率提升。· &n

- 關(guān)鍵字: Arm IP Explorer

英特爾 Arrow Lake 桌面處理器 LGA-1851 接口詳細(xì)規(guī)格曝光

- IT之家 7 月 18 日消息,國(guó)外科技媒體 Igor's LAB 日前爆料,Arrow Lake-S 將采用酷睿 Ultra 品牌,CPU 提升可達(dá) 21%,新架構(gòu)的核顯性能也會(huì)翻倍。Arrow Lake-S 旗艦型號(hào)也是 8 大核 + 16 小核的設(shè)計(jì),與當(dāng)前旗艦 i9-13900K 相同,此前消息稱還有 8+32 核心配置的型號(hào)。在最新報(bào)道中,詳細(xì)披露了英特爾 LGA 1851 插槽的全部細(xì)節(jié),IT之家在此附上鏈接,感興趣的用戶可以深入閱讀。英特爾 LGA 1851 插槽整體上接近

- 關(guān)鍵字: 英特爾 CPU

三星Exynos 2400芯片規(guī)格曝光:10個(gè)CPU核心 超過驍龍8 Gen 3

- 近日,有消息稱三星的新款芯片Exynos 2400 SoC將擁有10個(gè)CPU核心,其GPU基準(zhǔn)測(cè)試部分得分甚至超過了驍龍8 Gen 3。然而,三星Exynos 2400 SoC的最終配置和封裝信息目前仍未確定,三星正在權(quán)衡SoC的選擇,但預(yù)計(jì)該芯片將在明年的三星旗艦Galaxy S24系列中亮相。 雖然Exynos 2400 SoC將擁有10個(gè)CPU核心,但這10個(gè)核心并不會(huì)同時(shí)運(yùn)行,芯片將根據(jù)每個(gè)任務(wù)的需要,調(diào)度所需的核心數(shù)量。此外,最初的傳言稱Exynos 2400將采用Fo-WLP或Fan-out晶

- 關(guān)鍵字: 三星 Exynos 2400 CPU 8 Gen3

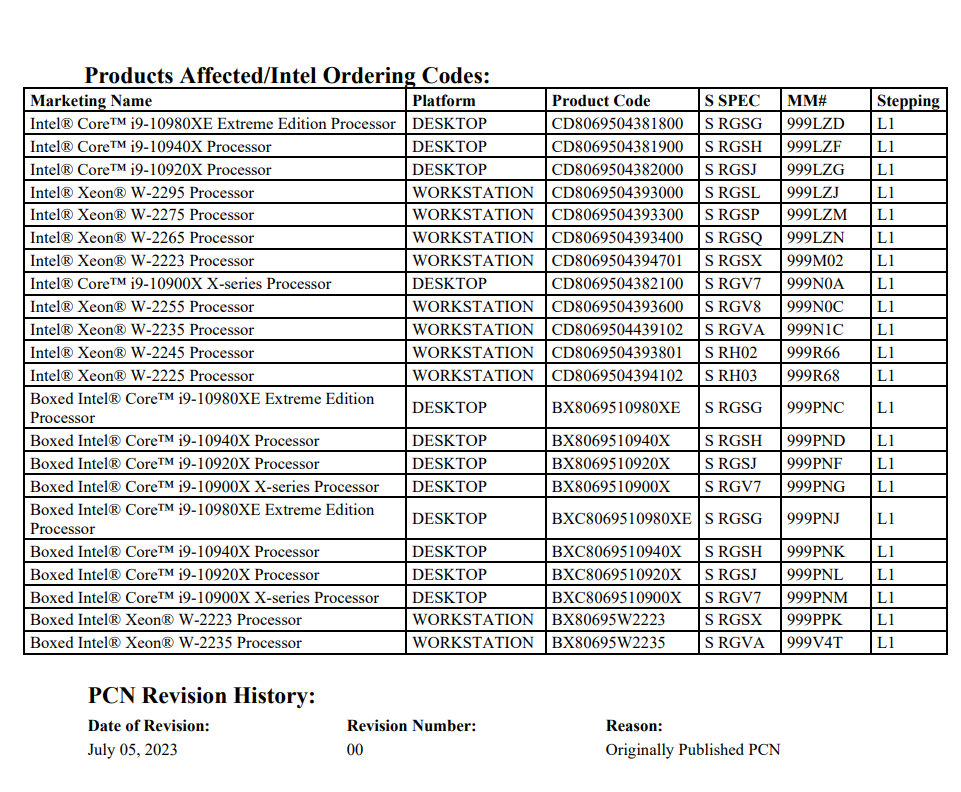

英特爾停產(chǎn) Cascade Lake-X / W 處理器,逐步清退最后一批 HEDT 產(chǎn)品

- IT之家 7 月 7 日消息,由于來自 AMD EPYC Rome 系列的激烈競(jìng)爭(zhēng),英特爾此前停產(chǎn)了部分 Cascade Lake Xeon 處理器,不過還有許多 Cascade Lake 型號(hào)幸免于難。而現(xiàn)在,英特爾決定砍掉部分剩余的“幸存者”。英特爾于 2019 年推出 Cascade Lake 來取代 Skylake 處理器,采用 14nm 工藝制造,包括用于 HEDT 的 Cascade Lake-X、用于工作站的 Cascade Lake-W 以及用于服務(wù)器的 Cascade Lake

- 關(guān)鍵字: 英特爾 CPU

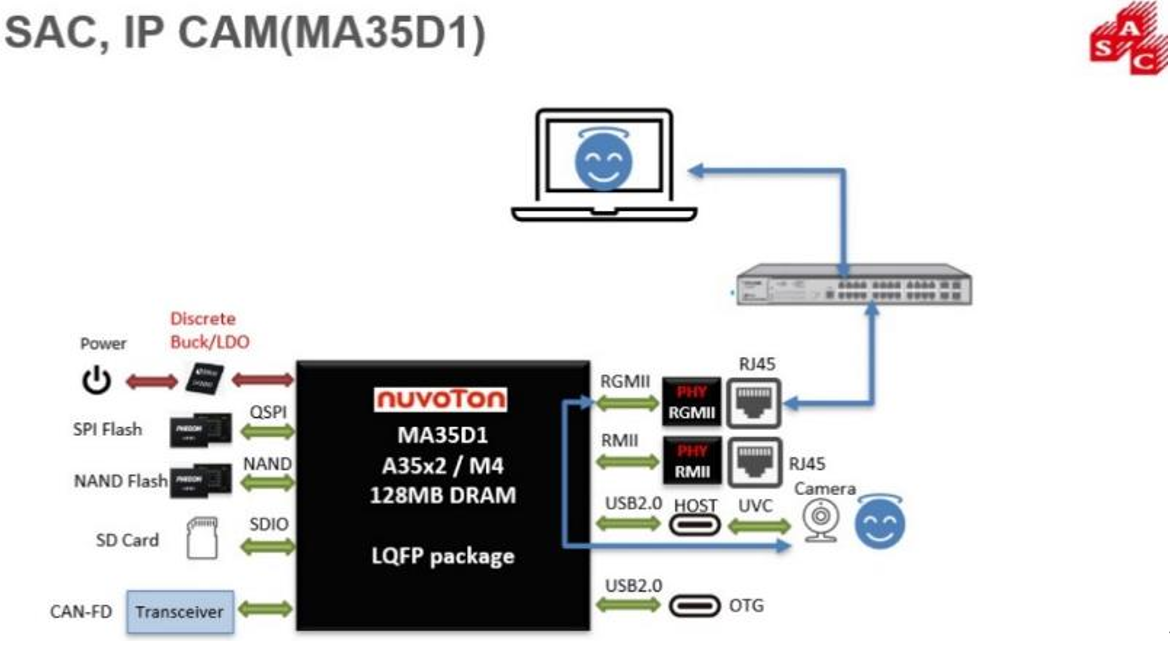

大聯(lián)大品佳集團(tuán)推出基于芯唐科技產(chǎn)品的IP CAM方案

- 2023年7月6日,致力于亞太地區(qū)市場(chǎng)的國(guó)際領(lǐng)先半導(dǎo)體元器件分銷商---大聯(lián)大控股宣布,其旗下品佳推出基于芯唐科技(Nuvoton)MA35D1芯片的IP CAM方案。 圖示1-

- 關(guān)鍵字: 大聯(lián)大品佳 芯唐 IP CAM

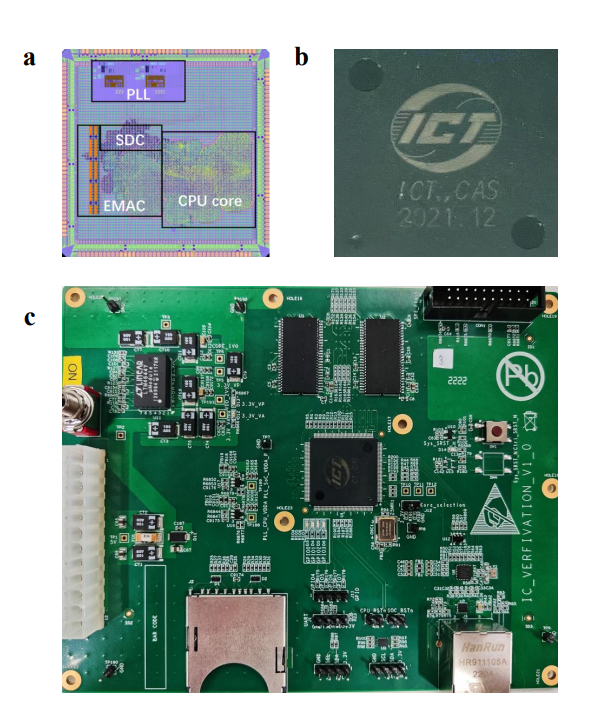

中國(guó)團(tuán)隊(duì)推出世界首顆 AI 全自動(dòng)設(shè)計(jì) CPU“啟蒙 1 號(hào)”:無人工干預(yù),性能堪比 486

- IT之家 6 月 30 日消息,據(jù)《半導(dǎo)體產(chǎn)業(yè)縱橫》報(bào)道,中科院計(jì)算所等機(jī)構(gòu)用 AI 技術(shù)設(shè)計(jì)出了世界上首個(gè)無人工干預(yù)、全自動(dòng)生成的 CPU 芯片 —— 啟蒙 1 號(hào)。該 CPU 基于 RISC-V 的 32 位架構(gòu),其相比于 GPT-4 目前能夠設(shè)計(jì)的電路規(guī)模大 4000 倍,性能與 Intel 486 系列 CPU 相當(dāng),可運(yùn)行 Linux 操作系統(tǒng)。▲ 圖源中科院計(jì)算所論文這是全球首個(gè)無人工干預(yù)、全自動(dòng)生成的 CPU 芯片,65nm 工藝,頻率達(dá)到了 300MHz,相關(guān)研究論文已經(jīng)在今年

- 關(guān)鍵字: RISC-V CPU AI

新思科技與三星擴(kuò)大IP合作,加速新興領(lǐng)域先進(jìn)SoC設(shè)計(jì)

- 摘要:●? ?新思科技接口IP適用于USB、PCI Express、112G以太網(wǎng)、UCIe、LPDDR、DDR、MIPI等廣泛使用的協(xié)議中,并在三星工藝中實(shí)現(xiàn)高性能和低延遲●? ?新思科技基礎(chǔ)IP,包括邏輯庫、嵌入式存儲(chǔ)器、TCAM和GPIO,可以在各先進(jìn)節(jié)點(diǎn)上提供行業(yè)領(lǐng)先的功耗、性能和面積(PPA)●? ?新思科技車規(guī)級(jí)IP集成到三星的工藝中,有助于確保ADAS、動(dòng)力總成和雷達(dá)SoC的長(zhǎng)期運(yùn)行并提高可靠性●? ?三星工藝中

- 關(guān)鍵字: 新思科技 三星 IP SoC設(shè)計(jì)

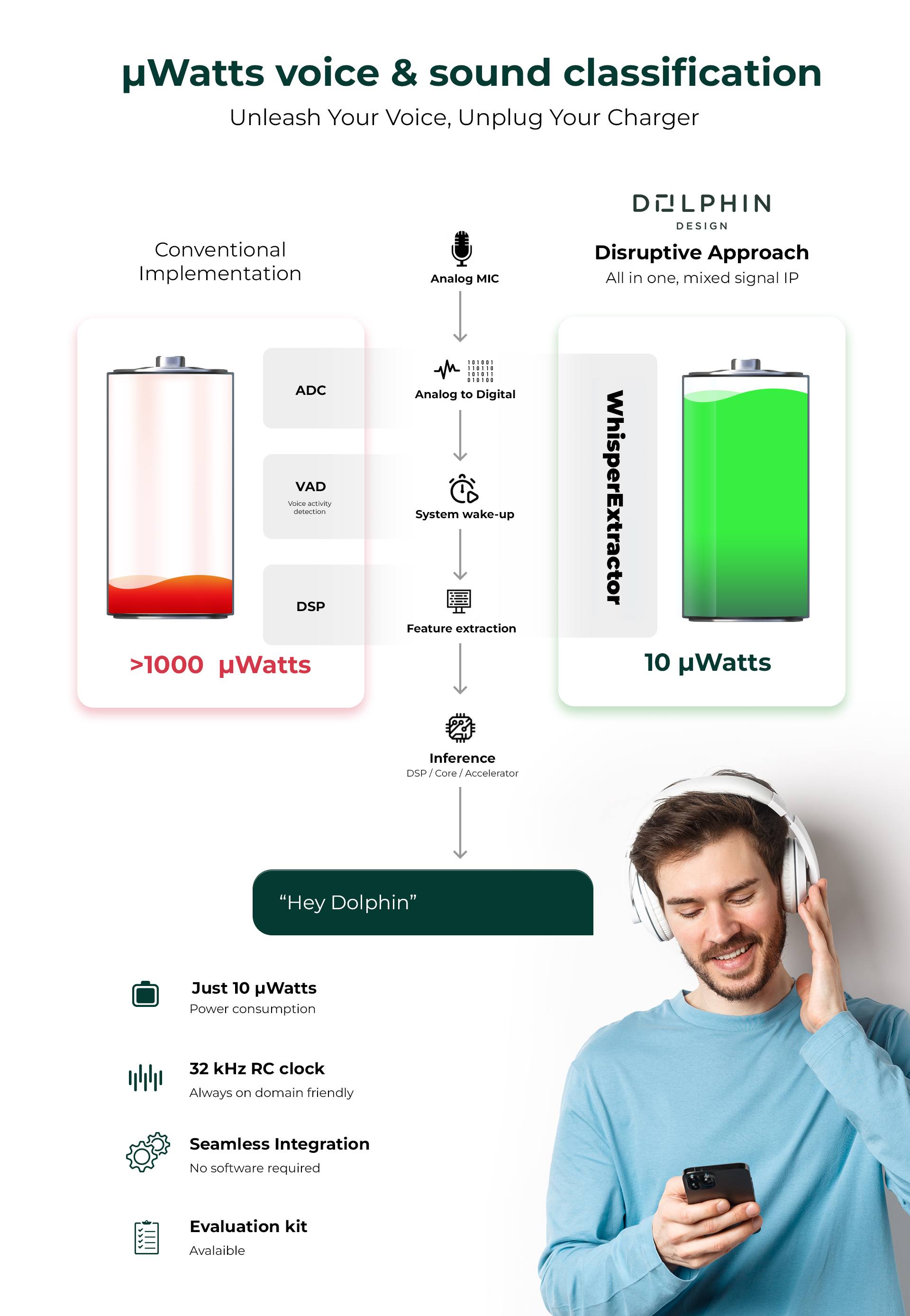

Dolphin Design推出用于聲音分類的創(chuàng)新IP,可減少99%的功耗

- Dolphin Design是提供電源管理、音頻和處理器以及ASIC設(shè)計(jì)服務(wù)的半導(dǎo)體IP解決方案的領(lǐng)導(dǎo)者,今天宣布推出WhisperExtractor,這是一個(gè)改變游戲規(guī)則的混合信號(hào)IP,用于支持語音和音頻的SoC。WhisperExtractor IP能夠以μW級(jí)別的功耗實(shí)現(xiàn)語音和聲音分類,為突破性的在線語音用戶界面和在線聲音檢測(cè)鋪平道路。該IP增強(qiáng)了旨在實(shí)現(xiàn)關(guān)鍵詞識(shí)別(KWS)、自動(dòng)語音識(shí)別(ASR)、自然語言處理(NLP)或智能安全攝像頭等電池供電的高能效聲音分類應(yīng)用。WhisperExtracto

- 關(guān)鍵字: Dolphin Design 聲音分類 IP

Dolphin Design推出用于聲音分類的創(chuàng)新IP,可減少99%的功耗

- 2023年6月28日,格勒諾布爾。Dolphin Design是提供電源管理、音頻和處理器以及ASIC設(shè)計(jì)服務(wù)的半導(dǎo)體IP解決方案的領(lǐng)導(dǎo)者,今天宣布推出WhisperExtractor,這是一個(gè)改變游戲規(guī)則的混合信號(hào)IP,用于支持語音和音頻的SoC。WhisperExtractor IP能夠以μW級(jí)別的功耗實(shí)現(xiàn)語音和聲音分類,為突破性的在線語音用戶界面和在線聲音檢測(cè)鋪平道路。該IP增強(qiáng)了旨在實(shí)現(xiàn)關(guān)鍵詞識(shí)別(KWS)、自動(dòng)語音識(shí)別(ASR)、自然語言處理(NLP)或智能安全攝像頭等電池供電的高能效聲音分類應(yīng)

- 關(guān)鍵字: Dolphin Design 聲音分類 IP

CEVA將在上海世界移動(dòng)通信大會(huì)展示消費(fèi)類電子用芯片和軟件IP

- 全球領(lǐng)先的無線連接和智能感知技術(shù)及共創(chuàng)解決方案的授權(quán)許可廠商CEVA, Inc.(納斯達(dá)克股票代碼:CEVA)參加2023年6月28至30日在上海舉辦的世界移動(dòng)通信大會(huì)。在這次展會(huì)上,CEVA團(tuán)隊(duì)將與SoC和OEM客戶面對(duì)面溝通交流,探討最新的技術(shù)創(chuàng)新,并介紹如何充分利用CEVA IP開發(fā)無線連接和智能感知應(yīng)用以實(shí)現(xiàn)產(chǎn)品設(shè)計(jì)目標(biāo)。 CEVA將在行政會(huì)議室展示用于邊緣AI、5G、計(jì)算機(jī)視覺、空間音頻(spatial-audio)和物聯(lián)網(wǎng)連接的最新解決方案,包括: ● 邊緣AI推

- 關(guān)鍵字: CEVA 上海世界移動(dòng)通信大會(huì) IP

英特爾新一代處理器命名爆料:RPL-R 為 14 代酷睿,MTL 另有其名

- IT之家 6 月 8 日消息,英特爾即將在今年晚些時(shí)候發(fā)布新一代處理器,其中包括 13代酷睿 Raptor Lake 的 Refresh 改進(jìn)版以及全新的 Meteor Lake 處理器。據(jù)推特用戶 harukaze5719 爆料,RPL-R 處理器的桌面版、H / HX、P 系列將被稱為 14 代酷睿,U / Y 系列仍被稱為 13代酷睿。MTL 采用了全新的命名方式,可能不會(huì)列入 XX 代酷睿的體系。據(jù)IT之家早前的報(bào)道,MTL 系列處理器已經(jīng)曝光的型號(hào)有 Ultra 5

- 關(guān)鍵字: 英特爾 CPU

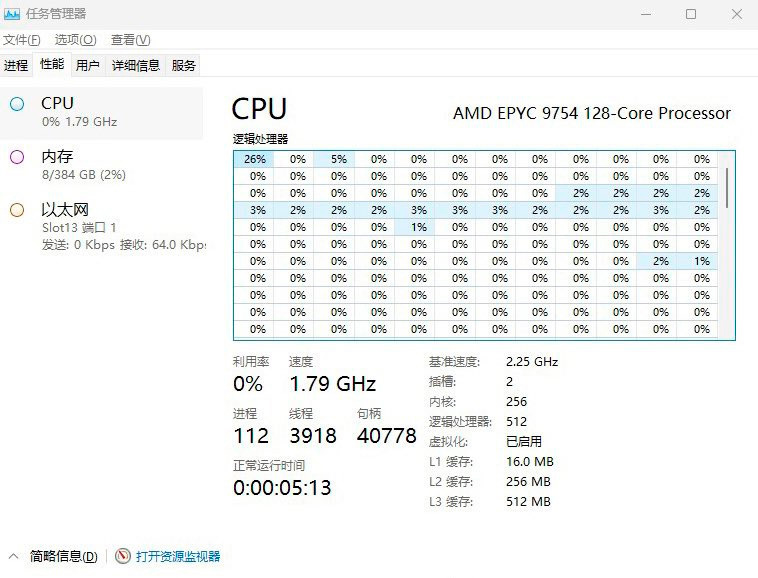

128 個(gè) Zen 4c 核心、256 MB L3 緩存,消息稱 AMD 下周推出 Bergamo 處理器

- IT之家 6 月 6 日消息,消息稱 AMD 將于下周推出首款采用 x86 架構(gòu)、具備 128 個(gè)核心的處理器--Bergamo。消息稱 Bergamo 處理器可以容納最多 128 個(gè) Zen 4c 核心,L3 緩存容量達(dá)到 256MB。Bergamo 處理器定位是 Core Zen 4 架構(gòu)的分支,主要為多核心場(chǎng)景設(shè)計(jì),預(yù)估將于 6 月 13 日舉辦的數(shù)據(jù)中心和人工智能技術(shù)首映式上亮相。可靠消息源 @momomo_us 分享了關(guān)于 Bergamo 處理器的更多信息,顯示會(huì)有 2 個(gè)版

- 關(guān)鍵字: AMD CPU

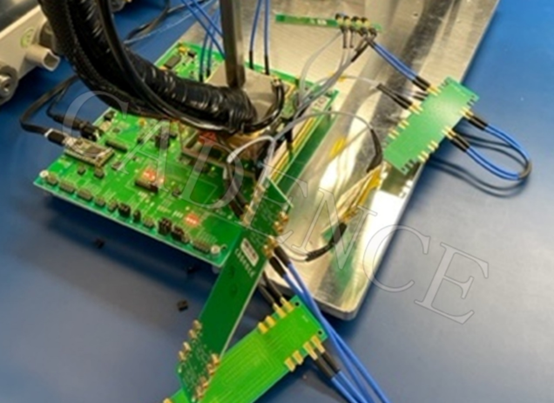

Cadence發(fā)布面向TSMC 3nm工藝的112G-ELR SerDes IP展示

- 3nm 時(shí)代來臨了!Cadence 在 2023 年 TSMC 北美技術(shù)研討會(huì)期間發(fā)布了面向臺(tái)積電 3nm 工藝(N3E)的 112G 超長(zhǎng)距離(112G-ELR)SerDes IP 展示,這是 Cadence 112G-ELR SerDes IP 系列產(chǎn)品的新成員。在后摩爾時(shí)代的趨勢(shì)下,F(xiàn)inFET 晶體管的體積在 TSMC 3nm 工藝下進(jìn)一步縮小,進(jìn)一步采用系統(tǒng)級(jí)封裝設(shè)計(jì)(SiP)。通過結(jié)合工藝技術(shù)的優(yōu)勢(shì)與 Cadence 業(yè)界領(lǐng)先的數(shù)字信號(hào)處理(DSP)SerDes 架構(gòu),全新的 112G-ELR

- 關(guān)鍵字: Cadence TSMC 3nm工藝 SerDes IP

cpu ip介紹

您好,目前還沒有人創(chuàng)建詞條cpu ip!

歡迎您創(chuàng)建該詞條,闡述對(duì)cpu ip的理解,并與今后在此搜索cpu ip的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)cpu ip的理解,并與今后在此搜索cpu ip的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司