- 全球電子設計創新領先企業Cadence設計系統公司宣布中國領先的無工廠半導體公司上海華虹集成電路有限責任公司(以下簡稱華虹設計)已經采用多種Cadence解決方案及服務,為中國快速發展的電子市場設計高級芯片。華虹設計之所以采用Cadence的技術,是看中其技術實力,包括可制造性設計(DFM)的低功耗與模擬/射頻產品,以及Cadence的技術支持服務的優勢。

華虹設計目前已經獲得Cadence多種產品與解決方案的使用權,包括Cadence Incisive 功能驗證、Encounter 數字IC設

- 關鍵字:

華虹 Cadence Virtuoso

- 全球電子設計創新領導廠商Cadence益華電腦今天宣布,創意電子(Global Unichip Corporation,GUC)將以CPF為基礎的Cadence低功耗解決方案,整合至其PowerMagic設計方法中,協助客戶將復雜的低功耗ASIC設計實現最佳化。

創意電子在PowerMagicTM設計方法,針對ASIC設計驗證與實現,整合Cadence®低功耗解決方案 (包括Cadence Encounter® RTL Compiler、Encounter 數位設計實現系統(ED

- 關鍵字:

Cadence PowerMagic 低功耗 EDI

- 摘 要:結合一個2.4 GHz CMOS低噪聲放大器(LNA)電路,介紹如何利用Cadence軟件系列中的IC 5.1.41完成CMOS低噪聲放大器設計。首先給出CMOS低噪聲放大器設計的電路參數計算方法,然后結合計算結果,利用Cadence軟件

- 關鍵字:

Cadence COMS 低噪聲放大器

- 全球電子設計創新領先企業Cadence設計系統公司(Nasdaq: CDNS)與全球最大的專業積體電路制造服務公司-臺灣積體電路制造股份有限公司(TWSE: 2330 , NYSE: TSM) (以下簡稱臺積公司)今日共同宣布推出業界第一款的混合信號/射頻參考設計”錦囊”(MS/RF RDK)。這款錦囊采用Cadence? Virtuoso?混合信號技術研發完成,可提供矽芯片特性行為模型(silicon-characterized behavioral mode

- 關鍵字:

Cadence 納米 混合信號

- 全球設計創新領先企業Cadence設計系統公司今天宣布上海東好科技發展有限公司(東好科技)已正式加盟Cadence®渠道伙伴計劃,成為一家增值代理商(VAR)。這一合作讓專注于中國EDA軟件先進技術與服務的東好科技能夠為國內設計師提供更豐富的途徑使用Cadence Allegro® PCB與IC封裝工具和技術。東好科技加入渠道伙伴計劃后,Cadence擴大了滿足中國本地設計團隊客戶需求的能力,并加強了其對全球客戶提供支持的承諾。

“我們很自豪也很興奮能夠成為Caden

- 關鍵字:

Cadence 集成電路

- Cadence設計系統公司和NEC電子公司,宣布開發出NEC電子公司基于業界最先進水平的V850™的System LSI的原型。它是在Cadence最新的Encounter數字實現系統(Encounter Digital Implementation System)8.1版本的支持下實現的。 NEC電子開發出其LSI下一代的CPU核,成功地降低了50%的設計周期(TAT),同時在整個設計流程后端包含了完全的全多模多角分析和優化。

自1996年4月推出第一款帶V850核心的單芯片微控制

- 關鍵字:

Cadence LSI NEC

- 【中國上海,2009年3月23日】- 全球設計創新領先企業Cadence設計系統公司(NASDAQ: CDNS),今天宣布世界級數字電視與視頻處理解決方案系統級芯片IC供應商華亞微電子有限公司 ( 華亞微 )已經實現一次性芯片成功,目前已經將一個面向液晶電視市場的0.162微米系統級芯片設計投入量產,實現了超過10%的尺寸縮減程度。

華亞微在選擇了Cadence作為其首要的EDA供應商,并采用Cadence端到端企業解決方案后實現了此次成功,為高清電視、機頂盒和多媒體市場提供高性能芯片。該公

- 關鍵字:

Cadence Encounter Incisive Virtuoso

- 【中國上海,2009年3月23日】Cadence設計系統公司(NASDAQ:CDNS),今天宣布世界級數字電視與視頻處理解決方案系...

- 關鍵字:

Cadence 力亞微 數字電視

- 1、概要 在進行PCB SI的設計時,理解特性阻抗是非常重要的。這次,我們對特性阻抗進行基礎說明之外,還說明Allegro的阻抗計算原理以及各參數和阻抗的關系。2、什么是特性阻抗?2.1 傳送線路的電路特性 在高頻

- 關鍵字:

Cadence PCB 分析 變化

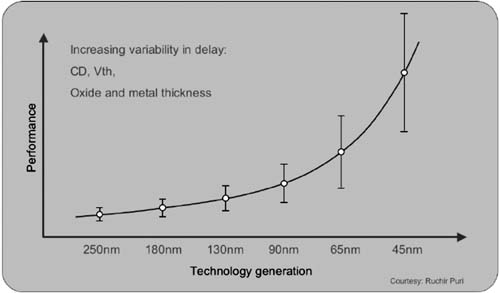

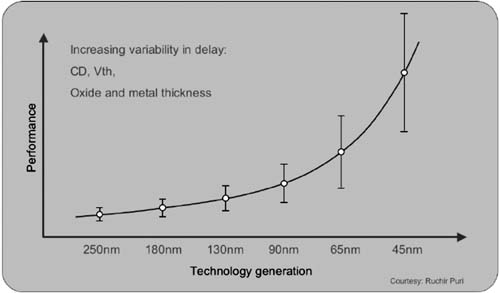

- 在一個依靠消費者對更精密產品的需求越來越高的市場里,半導體公司正在迅速地向45納米、以及更小的高級工藝節點發展。這些技術帶來了芯片質量和性能的大大提升,在系統級芯片上實現了更高級的復雜應用功能整合程度。然而,隨著更多的設計進化到高級技術,半導體公司面臨的設計挑戰也在激增,無法確保迅速量產的風險也在提高。

- 關鍵字:

Cadence ICs GDSII

- 在經歷了去年廣受矚目的收購風波之后,很長一段時間人們都對Cadence的前途感到憂心忡忡。而在Michael Fister黯然離職后,這種擔心被進一步的放大了。不過,目前看來這種擔心似乎是多慮了——Cadence亞太區總裁兼全球副總裁居龍不久前表示,其所屬的這家公司目前財務狀況良好。在歲末年初之時,他用一個“變”字來概括Cadence在2008年的表現。并表示新年Caden

- 關鍵字:

Cadence IC 數模混合 低功耗

- 【加州圣荷塞2008年12月16日】全球電子設計創新領先企業Cadence設計系統公司(納斯達克:CDNS),今天宣布推出Cadence® Virtuoso® Accelerated Parallel Simulator (APS), 這是其新一代電路仿真器,具有業界常用的Virtuoso Spectre® Circuit Simulator的完整精確性,用于解決所有工藝節點中最大型與最復雜的模擬與混合信號設計。作為Cadence多模式仿真解決方案(Cadence Multi-

- 關鍵字:

Cadence 電路仿真器

- 【加州圣荷塞2008年12月16日】全球電子設計創新領先企業Cadence設計系統公司(納斯達克:CDNS),今天宣布推出Cadence® Virtuoso® Accelerated Parallel Simulator (APS), 這是其新一代電路仿真器,具有業界常用的Virtuoso Spectre® Circuit Simulator的完整精確性,用于解決所有工藝節點中最大型與最復雜的模擬與混合信號設計。作為Cadence多模式仿真解決方案(Cadence Multi-

- 關鍵字:

Cadence 模擬與混合信號設計 仿真

cadence介紹

EDA仿真軟件Cadence

--------------------------------------------------------------------------------

Cadence Design Systems Inc.是全球最大的電子設計技術(Electronic Design Technologies)、程序方案服務和設計服務供應商。其解決方案旨在提升和監控半導 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473