EEPW首頁(yè) >>

主題列表 >>

cadence reality

cadence reality 文章 最新資訊

全新Cadence Virtuoso系統(tǒng)設(shè)計(jì)平臺(tái)幫助實(shí)現(xiàn)IC、封裝和電路板無(wú)縫集成的設(shè)計(jì)流程

- 楷登電子(美國(guó)Cadence公司)今日發(fā)布全新Cadence? Virtuoso? System Design Platform(Virtuoso系統(tǒng)設(shè)計(jì)平臺(tái)),結(jié)合Cadence Virtuoso平臺(tái)與Allegro? 及Sigrity?技術(shù),打造一個(gè)正式的、優(yōu)化的自動(dòng)協(xié)同設(shè)計(jì)與驗(yàn)證流程。多項(xiàng)跨平臺(tái)技術(shù)的高度集成幫助設(shè)計(jì)工程師實(shí)現(xiàn)芯片、封裝和電路板的同步和協(xié)同設(shè)計(jì)。這一過(guò)程在此之前只能通過(guò)手動(dòng)完成,全新Virtuoso系統(tǒng)設(shè)計(jì)平臺(tái)可以實(shí)現(xiàn)流

- 關(guān)鍵字: Cadence Virtuoso

Cadence擴(kuò)展JasperGold平臺(tái)用于高級(jí)形式化RTL簽核

- 楷登電子(美國(guó)Cadence公司)今日正式發(fā)布JasperGold? 形式驗(yàn)證平臺(tái)擴(kuò)展版,引入高級(jí)形式化驗(yàn)證技術(shù)的JasperGold Superlint和Clock Domain Crossing (CDC)應(yīng)用,以滿足JasperGold形式驗(yàn)證技術(shù)在RTL設(shè)計(jì)領(lǐng)域的簽核要求。較現(xiàn)有驗(yàn)證解決方案,Superlint和CDC應(yīng)用提高了IP設(shè)計(jì)質(zhì)量,后期RTL變更最高減少80%, IP開(kāi)發(fā)時(shí)間縮短4周。如需了解更多關(guān)于JasperGold技術(shù)

- 關(guān)鍵字: Cadence RTL

Cadence數(shù)字、簽核與定制/模擬工具助力實(shí)現(xiàn)三星7LPP和8LPP工藝技術(shù)

- 楷登電子(美國(guó) Cadence 公司) 今日宣布其數(shù)字、簽核與定制/模擬工具成功在三星電子公司7LPP和8LPP工藝技術(shù)上實(shí)現(xiàn)。較前代高階工藝節(jié)點(diǎn)FinFET技術(shù),7LPP和8LPP工藝技術(shù)不僅進(jìn)一步優(yōu)化了功耗、性能和面積特性,擴(kuò)展能力也更為出色。目前,客戶已經(jīng)可以應(yīng)用下一代技術(shù)開(kāi)始早期設(shè)計(jì)。 Cadence定制/模擬、數(shù)字和簽核工具全面滿足三星工藝需求,支持實(shí)現(xiàn)7LPP和8LPP工藝技術(shù);三星客戶可開(kāi)發(fā)各類復(fù)雜的高階節(jié)點(diǎn)設(shè)計(jì),充分滿足移動(dòng)市場(chǎng)和其他垂直市場(chǎng)的應(yīng)用需求。

- 關(guān)鍵字: Cadence 7LPP

Cadence弄潮神經(jīng)網(wǎng)絡(luò),發(fā)布高性能DSP IP

- 作者 王瑩 近日,Cadence發(fā)布了首款面向汽車、監(jiān)控、無(wú)人機(jī)和移動(dòng)市場(chǎng)的神經(jīng)網(wǎng)絡(luò)DSP IP,引起了業(yè)界的關(guān)注。 Cadence公司Tensilica事業(yè)部資深市場(chǎng)群總監(jiān)Steve Roddy專程來(lái)到北京,向媒體介紹其特點(diǎn)。 在神經(jīng)網(wǎng)絡(luò)的器件方面,英偉達(dá)主宰了通用GPU。此次Cadence Tensilica發(fā)布的神經(jīng)網(wǎng)絡(luò)DSP IP則是面向嵌入式芯片。 通常其他友商的方案是面向一個(gè)卷積神經(jīng)網(wǎng)絡(luò)(CNN)層,而最新的Cadence Tensilica Vision C5 DSP由于可配置,可以面

- 關(guān)鍵字: Cadence 神經(jīng)網(wǎng)絡(luò)DSP IP Steve Roddy 201706

Cadence弄潮神經(jīng)網(wǎng)絡(luò),發(fā)布高性能DSP IP

- 近日,Cadence發(fā)布了首款面向汽車、監(jiān)控、無(wú)人機(jī)和移動(dòng)市場(chǎng)的神經(jīng)網(wǎng)絡(luò)DSP?IP,引起了業(yè)界的關(guān)注。 實(shí)際上,多家公司正在推出或研制神經(jīng)網(wǎng)絡(luò)IP、c/解決方案。Cadence的方案有何優(yōu)勢(shì)?Cadence公司Tensilica事業(yè)部資深市場(chǎng)群總監(jiān)Steve?Roddy為此專程來(lái)到北京,向媒體介紹其特點(diǎn)。 Vision?C5概況 在神經(jīng)網(wǎng)絡(luò)的器件方面,英偉達(dá)主宰了通用GPU。此次Cadence?Tensilica發(fā)布的神經(jīng)網(wǎng)絡(luò)DSP?IP則是面

- 關(guān)鍵字: Cadence 芯片

Cadence發(fā)布業(yè)界首款面向汽車、監(jiān)控、無(wú)人機(jī)和移動(dòng)市場(chǎng)的神經(jīng)網(wǎng)絡(luò)DSP IP

- 楷登電子(美國(guó)Cadence公司)今日正式公布業(yè)界首款獨(dú)立完整的神經(jīng)網(wǎng)絡(luò)DSP —Cadence? Tensilica? Vision C5 DSP,面向?qū)ι窠?jīng)網(wǎng)絡(luò)計(jì)算能力有極高要求的視覺(jué)設(shè)備、雷達(dá)/光學(xué)雷達(dá)和融合傳感器等應(yīng)用量身優(yōu)化。針對(duì)車載、監(jiān)控安防、無(wú)人機(jī)和移動(dòng)/可穿戴設(shè)備應(yīng)用,Vision C5 DSP 1TMAC/s的計(jì)算能力完全能夠勝任所有神經(jīng)網(wǎng)絡(luò)的計(jì)算任務(wù)。如需了解更多內(nèi)容,請(qǐng)參訪www.cadence.co

- 關(guān)鍵字: Cadence DSP

應(yīng)用Cadence Protium S1,晶晨半導(dǎo)體大幅縮短多媒體SoC軟硬件集成時(shí)間

- 楷登電子(美國(guó) Cadence 公司)今日宣布,憑借Cadence? Protium? S1 FPGA原型驗(yàn)證平臺(tái),晶晨半導(dǎo)體(Amlogic)成功縮短其多媒體系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì)的上市時(shí)間。基于Protium S1平臺(tái),晶晨加速實(shí)現(xiàn)了軟/硬件(HW/SW)集成流程,上市時(shí)間較傳統(tǒng)軟硬件集成工藝縮短 2 個(gè)月。如需了解Protium S1 FPGA原型設(shè)計(jì)平臺(tái)的詳細(xì)內(nèi)容,請(qǐng)?jiān)L問(wèn)www.cadence

- 關(guān)鍵字: Cadence Protium

Cadence發(fā)布7納米工藝Virtuoso先進(jìn)工藝節(jié)點(diǎn)擴(kuò)展平臺(tái)

- 楷登電子(美國(guó)Cadence公司)今日正式發(fā)布針對(duì)7nm工藝的全新Virtuoso® 先進(jìn)工藝節(jié)點(diǎn)平臺(tái)。通過(guò)與采用7nm FinFET工藝的早期客戶展開(kāi)緊密合作,Cadence成功完成了Virtuoso定制設(shè)計(jì)平臺(tái)的功能拓展,新平臺(tái)能幫助客戶管理由于先進(jìn)工藝所導(dǎo)致的更復(fù)雜的設(shè)計(jì)以及特殊的工藝效應(yīng)。新版Virtuoso先進(jìn)工藝平臺(tái)同樣支持所有主流FinFET先進(jìn)節(jié)點(diǎn),性能已得到充分認(rèn)證;同時(shí)提高了7nm工藝的設(shè)計(jì)效率。 為了應(yīng)對(duì)7nm設(shè)計(jì)的眾多技術(shù)挑戰(zhàn),Virtuoso先進(jìn)工藝平臺(tái)提供豐富

- 關(guān)鍵字: Cadence Virtuoso

【E課堂】簡(jiǎn)介:國(guó)內(nèi)流行的PCB設(shè)計(jì)軟件

- PCB設(shè)計(jì)軟件就是以電路原理圖為根據(jù),實(shí)現(xiàn)電路設(shè)計(jì)所需的功能。電路板的設(shè)計(jì)主要指版圖設(shè)計(jì),需要考慮元器件和連線的整體布局,包括內(nèi)部電子元件的優(yōu)化布局;金屬連線和通孔的優(yōu)化布局;電磁防護(hù);散熱等各種因素。優(yōu)秀的PCB設(shè)計(jì)能夠達(dá)到良好的電路性能和散熱性能,節(jié)約生產(chǎn)成本。PCB設(shè)計(jì)需要借助計(jì)算機(jī)輔助設(shè)計(jì)(EDA)實(shí)現(xiàn)。下面介紹幾款國(guó)內(nèi)流行的PCB設(shè)計(jì)軟件。 Protel/Altium Designer 國(guó)內(nèi)低端設(shè)計(jì)的主流,簡(jiǎn)單易學(xué),適合初學(xué)者。國(guó)內(nèi)使用protel還是有相當(dāng)有市場(chǎng),畢竟小公司

- 關(guān)鍵字: PADS Cadence

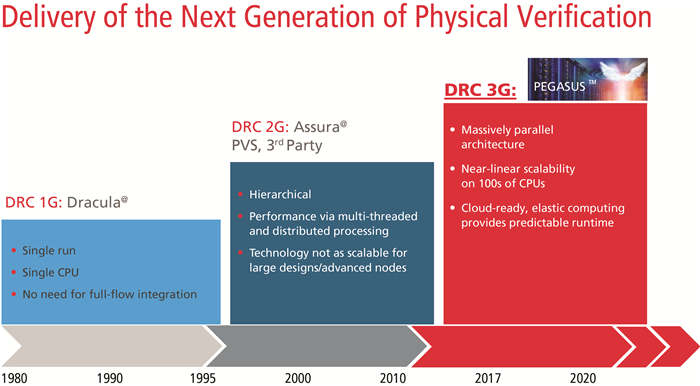

Cadence發(fā)布大規(guī)模并行物理簽核解決方案Pegasus驗(yàn)證系統(tǒng)

- 楷登電子(美國(guó) Cadence 公司)今日正式發(fā)布Pegasus?驗(yàn)證系統(tǒng),該云計(jì)算(cloud-ready)大規(guī)模并行物理簽核解決方案將助工程師縮短先進(jìn)節(jié)點(diǎn)IC的上市時(shí)間。Pegasus?驗(yàn)證系統(tǒng)解決方案是全流程Cadence數(shù)字設(shè)計(jì)與簽核套件的新成員,可擴(kuò)展至數(shù)百CPU,設(shè)計(jì)規(guī)則檢查(DRC)性能最高可提升10倍,周轉(zhuǎn)時(shí)間較上一代Cadence? 解決方案由數(shù)日降至數(shù)小時(shí)。如需了解Pegasus驗(yàn)證系統(tǒng)的詳細(xì)內(nèi)容,請(qǐng)參訪www.cadence.com/go/pegas

- 關(guān)鍵字: Cadence Pegasus

Cadence獲得TSMC 7nm工藝技術(shù)認(rèn)證

- 楷登電子(美國(guó) Cadence 公司,NASDAQ: CDNS)今日正式宣布與臺(tái)灣積體電路制造股份有限公司(TSMC)取得的多項(xiàng)合作成果,進(jìn)一步強(qiáng)化面向移動(dòng)應(yīng)用與高性能計(jì)算(HPC)平臺(tái)的7nm FinFET工藝創(chuàng)新。Cadence? 數(shù)字簽核與定制/模擬電路仿真工具獲得TSMC 7nm工藝 v1.0設(shè)計(jì)規(guī)則手冊(cè)(DRM)認(rèn)證及SPICE認(rèn)證。合作期間,Cadence開(kāi)發(fā)了包括多種解決方案的全新工藝設(shè)計(jì)包(PDK),進(jìn)一步實(shí)現(xiàn)功耗、

- 關(guān)鍵字: Cadence 7nm

Cadence與TSMC合作12FFC工藝技術(shù),驅(qū)動(dòng)IC設(shè)計(jì)創(chuàng)新

- 楷登電子(美國(guó) Cadence 公司)今日正式公布其與臺(tái)灣積體電路制造股份有限公司(TSMC)全新12nm FinFET緊湊型(12FFC)工藝技術(shù)開(kāi)發(fā)的合作內(nèi)容。憑借Cadence? 數(shù)字與Signoff解決方案、定制/模擬電路仿真解決方案及IP,系統(tǒng)級(jí)芯片(SoC)設(shè)計(jì)師可以利用12FFC工藝開(kāi)發(fā)正在快速發(fā)展的中端移動(dòng)和高端消費(fèi)電子應(yīng)用。上述應(yīng)用對(duì)PPA性能(功耗、性能和面積)的要求更高,為此,Cadence正與12FFC工藝的早期客戶開(kāi)展緊密合作。 Ca

- 關(guān)鍵字: Cadence TSMC

Cadence攜手CommSolid開(kāi)發(fā)全新NB-IoT基帶IP,進(jìn)軍移動(dòng)IoT市場(chǎng)

- 楷登電子(美國(guó) Cadence 公司)今日宣布,將與移動(dòng)IoT公司CommSolid展開(kāi)合作,為超低功耗移動(dòng)通訊環(huán)境開(kāi)發(fā)度身定制的全新基帶 IP,并結(jié)合最新發(fā)布的 3GPP 窄頻帶物聯(lián)網(wǎng)(NB-IoT)通訊標(biāo)準(zhǔn),發(fā)力迅速發(fā)展的移動(dòng)IoT市場(chǎng)。 CommSolid將單顆Cadence? Tensilica? Fusion F1 DSP與其最新CSN130基帶解決方案集成,用于超低功率modem運(yùn)行;以及包括語(yǔ)音觸

- 關(guān)鍵字: Cadence NB-IoT

cadence reality介紹

您好,目前還沒(méi)有人創(chuàng)建詞條cadence reality!

歡迎您創(chuàng)建該詞條,闡述對(duì)cadence reality的理解,并與今后在此搜索cadence reality的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)cadence reality的理解,并與今后在此搜索cadence reality的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司