- 0 引言紅外通信作為一種簡便的無線通信技術在電子設備中具有廣泛的應用。它的主要優點是無需專門申請特定頻率的使用執照;具有移動通信設備所必需的體積小,功率低的特點;傳輸速率適合家庭和辦公室使用的網絡;信號無干

- 關鍵字:

SoPC 紅外解碼 IP核 系統

- 隨著網絡技術與通信技術的高速發展,測試儀器和測試技術發生了革命性變化,“網絡就是儀器”確切地概括了測試儀器間的網絡化發展趨勢。組建網絡化測試系統不僅能實現資源共享,而且組建系統方便,還可提高

- 關鍵字:

GPIB 控制器 IP核 軟件

- 計算機科學技術中的數據加密是信息安全的重要手段。Rijndael加密算法由比利時密碼學家JoanDaemen和VincentRijmen發明的一種迭代型分組加密算法,2000年被確定為美高級加密標準AES的最終算法。本文通過對AES算法的流程

- 關鍵字:

AES 加解密 IP核 算法

- 上周在看了我的朋友Dave Jones拆解一臺舊的Fluke 91 ScopeMeter DSO(數字采樣示波器)的視頻時,我突然發現,這款有20年歷史的測試設備標志著ASIC設計歷時10年的衰落正開始顯著加速。

- 關鍵字:

賽靈思 ASIC ASSP ARM

- 隨著嵌入式技術的發展,基于SoPC技術的嵌入式系統所具有的軟硬件可裁減、可擴充、可升級以及可在線修改的特點越來越受到人們的重視。SoPC系統通常具有以下基本特征:采用大容量可編程邏輯器件來實現,單芯片、低功耗

- 關鍵字:

SOPC IP核 異步串行通信

- 富士通半導體(上海)有限公司于日前宣布其獲得海思半導體策略ASIC合作伙伴榮譽。富士通的高速IP解決方案和ASIC設計服務,是海思授予其這一榮譽的關鍵所在。

由于不斷升級的處理速度和越來越復雜的調制解調算法,現代通信芯片往往會集成數億個同時工作的晶體管和超高速的模擬互聯IP。而在這樣的芯片上,領先工藝所帶來的物理設計收斂會變得越來越困難,片上巨大規模的數字電路對超高速模擬IP的串擾也變得越來越明顯,如何在很短的設計周期內去盡可能的定義和優化全芯片的低功耗策略,如何協同考慮封裝設計來包容超高的功耗

- 關鍵字:

富士通 ASIC 半導體

- 可編程片上系統(SOPC)是一種特殊的嵌入式系統,它設計方式靈活,具備軟硬件在系統可編程功能。SOPC在設計上...

- 關鍵字:

SOPC 觸控屏控制器 IP核

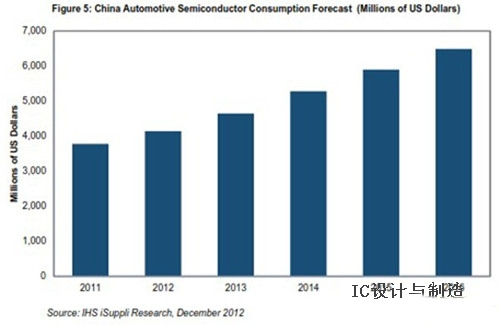

- 據IHS iSuppli公司的中國研究報告,盡管需求比前幾年放緩,但2012年中國汽車半導體市場仍有望強勁增長9.7%。政府激勵措施在第四季度促進了中國汽車市場的增長。

今年中國汽車半導體市場營業收入預計達到41億美元,高于2011年的38億美元。明年,中國總體汽車半導體營業收入將增長12%,達到46億美元。2011-2016年,中國汽車半導體市場的復合年度增長率將達11%,如圖所示。

?

圖:中國汽車半導體市場營業收入預測

這種增長令人鼓舞。中國消費者要求汽

- 關鍵字:

汽車 半導體 ASIC

- 分析了UART核的結構和智能卡的傳輸協議,提出一種基于UART核的智能卡接口IP核的設計。該設計以成熟的UART核為基礎,無需編寫異步串口的時序與接口邏輯,僅在串口核中增加收發緩沖器和協議處理等模塊,減少了工作量并縮短了開發周期。最后對所設計的IP核進行仿真和實際測試,結果表明該IP核設計正確,運行穩定,適合在多卡系統中應用。

- 關鍵字:

UART IP核 智能卡 接口

- 全球電子設計創新領先企業 Cadence 設計系統公司 (NASDAQ:CDNS) 日前宣布 Renesas 微系統有限公司已采用 Cadence? Encounter? RTL Compiler 用于綜合實現,尤其是將復雜 ASIC 設計的芯片利用率提高了 15%,面積減少了 8.4%,加速了實現周期并降低了成本。

- 關鍵字:

Cadence Renesas 微系統 ASIC

- 1概述

隨著集成電路(Integrated Circuit,IC)設計技術和工藝水平進入超深亞微米,集成電路規模越來越大,芯片設計規模和設計復雜度也急劇提高,工藝流程呈現專業化,EDA設計逐步發展和完善。九十年代出現了SoC芯片,即可

- 關鍵字:

SoC IP核

- SOPC(System on a Programmable Chip,片上可編程系統)是Altera公司提出的一種靈活、高效的SOC解決方案。它將處理器、存儲器、I/O接口、LVDS、CDR等系統設計需要的功能模塊集成到一個可編程邏輯器件上,構建一個可

- 關鍵字:

Nios DDS IP核 可重構

- 2012年11月14日,奧地利微電子宣布開始供應新款高集成ASIC,在較低的X射線劑量下,幫助西門子新型計算機斷層掃描(CT)光探測器模塊提供更高分辨率的圖像。奧地利微電子公司是全球領先的高性能模擬IC和傳感器解決方案的設計者及制造商,專為消費通信、醫療電子、汽車應用行業服務。

作為西門子新型Stellar CT光探測器模塊的組成部分,奧地利微電子的ASIC可捕捉并數字化病人身體的圖像。它在一個層疊骰子型(3D集成式)配置結構內,將一個高分辨率光電二極管同一個低噪聲模數轉換器(ADC)整合在了一

- 關鍵字:

西門子 ASIC CT

- 0.引言

FIR(Finite Impulse Response,有限沖擊響應)數字濾波器具有穩定性高、可以實現線性相位等優點,廣泛被應用于信號檢測與處理等領域[1,2]。由于FPGA(Field Programmable Gate Array,現場可編程門陣列)

- 關鍵字:

FIR IP核 低通濾波器

- 幾年前設計專用集成電路(ASIC) 還是少數集成電路設計工程師的事, 隨著硅的集成度不斷提高,百萬門的ASIC 已不難實現, 系統制造公司的設計人員正越來越多地采用ASIC 技術集成系統級功能(System L evel In tegrete - SL

- 關鍵字:

FPGA IP核 設計方法

asic ip核介紹

您好,目前還沒有人創建詞條asic ip核!

歡迎您創建該詞條,闡述對asic ip核的理解,并與今后在此搜索asic ip核的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473