基于UART的智能卡接口IP核設(shè)計(jì)

摘要:分析了UART核的結(jié)構(gòu)和智能卡的傳輸協(xié)議,提出一種基于UART核的智能卡接口IP核的設(shè)計(jì)。該設(shè)計(jì)以成熟的UART核為基礎(chǔ),無需編寫異步串口的時(shí)序與接口邏輯,僅在串口核中增加收發(fā)緩沖器和協(xié)議處理等模塊,減少了工作量并縮短了開發(fā)周期。最后對(duì)所設(shè)計(jì)的IP核進(jìn)行仿真和實(shí)際測(cè)試,結(jié)果表明該IP核設(shè)計(jì)正確,運(yùn)行穩(wěn)定,適合在多卡系統(tǒng)中應(yīng)用。

關(guān)鍵詞:UART;智能卡;IC卡;IP核;FPGA

引言

智能卡以其安全、靈活、通用等特點(diǎn),被廣泛應(yīng)用在金融、交通以及其他安全終端設(shè)備上。目前許多讀卡器都采用單片機(jī)來實(shí)現(xiàn),而在一些特殊應(yīng)用中,同時(shí)需要多張甚至10張以上的智能卡。由于卡片嚴(yán)格的時(shí)序要求,僅用單片機(jī)已經(jīng)很難實(shí)現(xiàn)多卡的并行操作。FPGA具有硬件并行性和可編程等優(yōu)點(diǎn),很容易實(shí)現(xiàn)并行且對(duì)時(shí)序邏輯要求較高的操作,同時(shí)IP核的應(yīng)用又給基于FPGA的開發(fā)帶來了極大的便利,能減少大量開發(fā)時(shí)間。

本文首先介紹了智能卡的基本規(guī)范,著重分析字符傳輸協(xié)議(T=0)的操作流程。然后分析了Altera公司提供的UART IP核的結(jié)構(gòu),在此基礎(chǔ)上給出了智能卡接口IP核的設(shè)計(jì),并結(jié)合智能卡的操作流程,給出了傳輸協(xié)議的狀態(tài)轉(zhuǎn)換圖以及實(shí)現(xiàn)方法。最后對(duì)IP核進(jìn)行仿真分析和實(shí)際測(cè)試。

1 智能卡操作流程簡(jiǎn)介

智能卡是IC卡的一種,帶有微處理器、存儲(chǔ)單元以及芯片操作系統(tǒng),不僅具有數(shù)據(jù)存儲(chǔ)功能,同時(shí)還具有命令處理和數(shù)據(jù)安全保護(hù)等功能。智能卡采用異步半雙工通信方式,其傳輸協(xié)議分為字符傳輸協(xié)議(T=0)和塊傳輸協(xié)議(T=1),本文重點(diǎn)討論字符傳輸協(xié)議(T=0),它是目前使用較廣泛的通信協(xié)議。

智能卡主要有復(fù)位操作和指令操作。復(fù)位操作是將智能卡的復(fù)位引腳拉低若干周期,拉高后智能卡回復(fù)1個(gè)數(shù)據(jù)幀,提供了協(xié)議選擇、時(shí)鐘轉(zhuǎn)換因子、波特率調(diào)整因子等參數(shù),可供后續(xù)操作使用。該幀的長(zhǎng)度在第2個(gè)字節(jié)中體現(xiàn),因此先接收2個(gè)字節(jié),再接收固定長(zhǎng)度的數(shù)據(jù),操作流程圖如圖1所示。

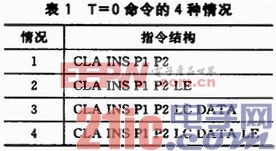

T=0時(shí),指令操作主要有4種情況,如表1所列。

根據(jù)中國(guó)金融集成電路(IC)卡規(guī)范的規(guī)定,可在情況1后面補(bǔ)0,組成5字節(jié)指令。這時(shí),4種情況都可歸納為:發(fā)送前5字節(jié),等待接收1字節(jié)回復(fù),由回復(fù)決定后續(xù)的操作。

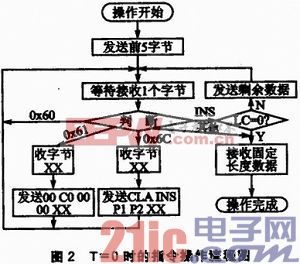

1字節(jié)的回復(fù)分為過程字節(jié)和狀態(tài)字節(jié)兩類,過程字節(jié)主要有INS(或INS補(bǔ)碼)、60、61、6C;除過程字節(jié)以外的其他回復(fù)都屬于狀態(tài)字節(jié)。收到過程字節(jié)后須執(zhí)行對(duì)應(yīng)操作。接收到狀態(tài)字節(jié)后須再等待接收1字節(jié)狀態(tài)回復(fù),將兩個(gè)狀態(tài)字節(jié)上傳給控制器,終止本次操作。T=0

時(shí)的指令操作流程圖如圖2所示。

2 智能卡接口IP核的設(shè)計(jì)與實(shí)現(xiàn)

2.1 UART核分析

UART接口已經(jīng)很成熟,已有許多現(xiàn)成的IP核可使用,利用UART進(jìn)行智能卡接口IP核的設(shè)計(jì)可減少大量的開發(fā)時(shí)間。本文以Altera公司的Avalon總線接口的UART核(下文中所有UART核均指該核)為基礎(chǔ)進(jìn)行設(shè)計(jì)。

評(píng)論