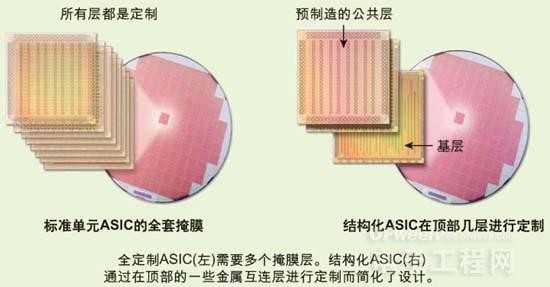

- 作為一個系統設計工程師,經常會遇到這個問題:是選用ASIC還是FPGA?讓我們來看一看這兩者有什么不同。所謂ASIC,是專用集成電路(Application Specific Integrated Circuit)的簡稱,電子產品中,應用非常廣泛。ASIC的

- 關鍵字:

FPGA ASIC 系統設計 成本因素

- 我經常收到關于各類設備之間的差異的問題,諸如ASIC、ASSP、SoC和FPGA之間的區別問題。例如是SoC是ASIC嗎?或ASIC是SoC嗎?ASIC和ASSP之間的區別是什么?以及高端FPGA應該歸類為SoC嗎?這里有幾個難題,至少技術和術語隨

- 關鍵字:

ASIC ASSP SoC FPGA

- 聯華電子今(12日)與ASIC設計服務暨IP研發銷售廠商智原科技(Faraday Technology Corporation,TWSE:3035)共同發表智原科技于聯電55奈米超低功耗製程(55ULP)的PowerSlash™基礎IP方案。智原PowerSlash™與聯電製程技術相互結合設計,為超低功耗的無線應用需求技術進行優化,滿足無線物聯網產品的電池長期壽命需求。

智原科技行銷暨投資副總于德旬表示:「物聯網應用建構過程中,效能往往受制于低功耗技術。而今透過聯電55奈

- 關鍵字:

聯華電子 ASIC

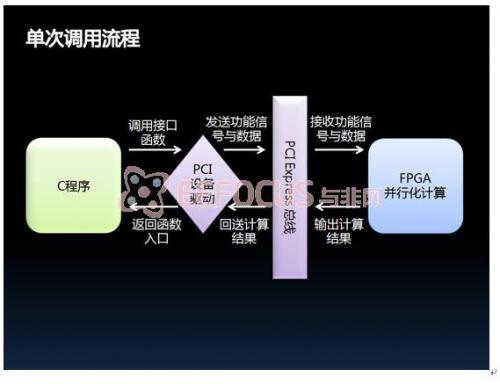

- 摘要 利用FPGA IP核設計了一種快速、高效的傅里葉變換系統。針對非整數倍信號周期截斷所導致的頻譜泄露問題,提出了一種通過時輸入信號加窗處理來抑制頻譜泄露的方法。利用Modelsim和Matlab對設計方案進行了仿真,同

- 關鍵字:

FFT FPGA IP核 加窗處理

- SOPC(System On a Programmable Chip,可編程芯片系統)就是在一個可編程芯片上實現一個電子系統的技術。SOPC是可編程邏輯器件技術和SoC(System on Chip)技術發展與

- 關鍵字:

Avalon總線 SHT11 溫濕度傳感器 IP核

- 數字化是電子設計發展的必然趨勢,EDA 技術綜合了計算機技術、集成電路等在不斷向前發展,給電子設計領域帶來了一種全新的理念。本文筆者首先簡

- 關鍵字:

EDA ASIC

- 一種CORDIC協處理器核的設計與實現, 隨著航天技術的發展,航天任務對于導航計算機的性能要求越來越高。導航計算機除了要對傳感器數據進行采集,與控制系統進行實時通訊,還要能進行實時的計算。盡管目前航天任務中使用的處理器芯片性能越來越強,但大多

- 關鍵字:

FPGA IP核 CORDIC 協處理器

- 本文通過列舉Altera 公司的 20nm Arria 10 FPGA 和 Arria 10 SoC (片上系統) 開發電路板的電源管理解決方案,分析了對于FPGA、GPU 或 ASIC 控制的系統中電源管理帶來的挑戰,并指出通過使用 LTPowerCAD 和 LTPowerPlanner 這類工具,可以大大簡化對負載點穩壓器以及各部分分析結果的映射任務。

- 關鍵字:

電源管理 FPGA GPU ASIC 201609

- ASIC 設計服務暨 IP 研發銷售領導廠商-智原科技(Faraday Technology, TAIEX: 3035)于日前獲頒 ISO9001 Plus 典范獎項。ISO9001:2015是ISO 15年來最大改版,能成為首批獲得SGS專業驗證的廠商,是對智原在品質承諾、經營與職能發展表現上的高度肯定和最具體驗證。

智原科技成立于1993年,累積20余年在 IP (矽智財)與 ASIC 設計服務的豐富經驗,不但自主產出了3,000多支的 IP,更有2,000多個專案的成功量產經驗,客戶遍及臺

- 關鍵字:

ASIC 智原科技

- 聯華電子今(3日) 與 ASIC 設計服務暨 IP 研發銷售廠商智原科技共同發表智原科技于聯電28奈米 HPCU 工藝的可編程12.5Gbps SerDes PHY IP 方案。此次智原成功推出的 SerDes PHY,為聯電28奈米 High-K / Metal Gate 后閘極技術工藝平臺中一系列高速 I/O 解決方案的第一步。

藉由采用涵蓋1.25Gbps 到12.5Gbps 的可編程架構技術,此 SerDes PHY 能夠輕易支持10G/1G xPON 被動光纖網絡通訊設備。結合不同的

- 關鍵字:

聯華電子 ASIC

- Arasan今日宣布,其MIPI DPHY IP核Ver1.2版本即刻開始供貨,該版本在TSMC 28納米HPC工藝之上可支持高達2.5Gbps的速度。該IP產品將很快被移植到TSMC最新的HPC Plus工藝上。Arasan的MIPI DPHY IP核向下兼容以前的標準版本,需要時能夠以1.5Gbps或更低的速度運行。

Arasan提供的最新DPHY IP產品使用了全新的、正在申請專利的DPHY架構,該架構為實現超低功耗和超小面積而優化了DPHY設計。

“我們利用自己在DPH

- 關鍵字:

Arasan IP核

- 靜態時序分析簡稱STA(Static Timming Analysis),它提供了一種針對大規模門級電路進行時序驗證的有效方法。它指需要更具電路網表的拓撲,就可以檢查電路設計中所有路徑的時序特性,測試電路的覆蓋率理論上可以達到100%,從而保證時序驗證的完備性;同時由于不需要測試向量,所以STA驗證所需時間遠小于門級仿真時間。但是,靜態時序分析也有自己的弱點,它無法驗證電路功能的正確性,所以這一點必須由RTL級的功能仿真來保證,門級網表功能的正確性可以用門級仿真技術,也可以用后面講到的形式驗證技術。值

- 關鍵字:

fpga asic 靜態時序

- 除法,這個小學4年紀就開始學習和使用的方法卻一直是我這個ASIC工程師心中的痛。我一直在思考如何能找到一個簡單(硬件資源少)而快捷(時鐘排數少)的通用除法電路。 其實簡單的說除法可以用迭代的減法來實現,但是對于硬件,這恐怕要花很多時間。我也一直沒有找到實現任意除法的好方法。但是對于某些除數固定的除法還是有一些辦法的。 1)最容易想到的就是ROM查找表,但是ROM畢竟不是我們的目標,雖然ROM有時是不錯的方法。 2)我開始仔細考慮這個問題是在做264解碼時必須要處理QP的問題。這是一個除以6的計算

- 關鍵字:

除法電路 ASIC

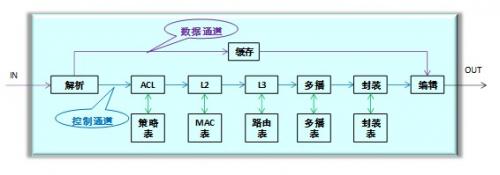

- 2015年10月19日,Mentor Graphics公司今天宣布,推出支持25G、50G和100G以太網的Veloce® VirtuaLAB Ethernet環境。這種支持有助于實現今天正在創建的基于大規模以太網設計的高效的、基于仿真的驗證。

連接需求的激增對交換機和路由器設計的尺寸有著深遠的影響,使之成為了今天開發的最大的IC設計。設計的絕對尺寸、早期發布的壓力,以及需要驗證所有路徑,都推動著將驗證從模擬轉向基于仿真流程方法的轉變。

Juniper Networks硅和系統工程

- 關鍵字:

Mentor Graphics ASIC

- 西昌發射的兩顆新一代北斗導航衛星近日來成為國內各方關注的焦點,在這兩顆衛星和“遠征一號”火箭上,不僅100%使用了中國自主開發的宇航CPU芯片,還承載著數據總線電路、轉換器、存儲器等大量其他國產芯片。據了解,這是中國衛星第一次成體系地批量使用國產芯片。

- 關鍵字:

北斗 ASIC

asic ip核介紹

您好,目前還沒有人創建詞條asic ip核!

歡迎您創建該詞條,闡述對asic ip核的理解,并與今后在此搜索asic ip核的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473