基于FPGA IP核的FFT實現與改進

摘要 利用FPGA IP核設計了一種快速、高效的傅里葉變換系統。針對非整數倍信號周期截斷所導致的頻譜泄露問題,提出了一種通過時輸入信號加窗處理來抑制頻譜泄露的方法。利用Modelsim和Matlab對設計方案進行了仿真,同時在Altera公司的CycloneⅡ硬件平臺上進行了驗證。驗證結果表明,系統性能良好,改進效果明顯。

本文引用地址:http://www.104case.com/article/201610/306475.htmFFT是離散傅里葉變換(DFT)的一種快速算法,被廣泛應用于頻譜分析、音頻編碼、圖像處理等數字信號處理領域。FFT運算復雜,需要大量的存儲器和運算單元,其硬件實現平臺多種多樣。DSP需要外置存儲器和特定接口,限制了運算速度。ASIC雖能滿足速度要求,但其硬件電路復雜、可擴展性差、且價格昂貴。FPGA具有陜速并行運算、高集成度、低功耗等特點,且具有豐富的IP核資源,方便調用,適合FFT算法的實現。

對于512點FFT處理器,如果該512個輸入數據不是信號周期的整數倍,即非整數倍周期截斷,則會出現頻譜泄露現象。窗函數處理的宗旨是減小頻譜泄露。常規的FFT硬件實現方法均不考慮由于非整數倍截斷導致的頻譜泄露問題。針對以上問題,本文設計了一種基于Altera IP核的512點FFT系統,同時通過對輸入信號的加窗處理,抑制了非整數倍信號周期截斷所產生的頻譜泄露。

1 原理概述

1.1 FFT原理

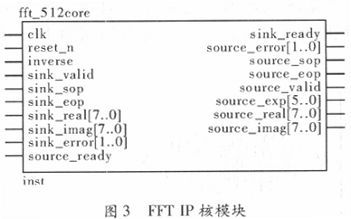

離散傅里葉變換(DFT)算法為

FFT為DFT的快速算法,其方法多種多樣,基本可以分為按時間抽取法和按頻率抽取法兩類。此處介紹基-4頻率抽取法。令N=4M,對式(1)N點的DFT可按如下方法作按頻率出抽取

4個等式可定義為一個蝶形運算,蝶形運算可看作基-4FFT基本運算單元。參與蝶形運算的4個節點是有規律的,分別為(n)、(n+N/4)、(n+2N/4)和(n+3N/4)。接著再將X(4r)、X(4r+1)、X(4r+2)和X(4r+3)分別分解為4個長度為N/16的序列,基本結構是每一級的運算由N/4個蝶形運算構成,經過迭代log4N次后完成計算。FFT算法的本質是利用系數

的共軛對稱性和周期性,將長序列DFT分解成短序列DFT,避免了大量的重復運算,從而提高運算效率。

1.2 窗函數原理

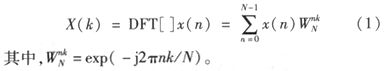

當對輸入信號非整數倍周期截斷,即512個輸入數據不是輸入信號周期的整數倍時,會出現頻譜泄露現象。對輸入信號進行加窗處理,可以有效地抑制頻譜泄露。常用的窗函數有矩形窗(Rectangle Window)、漢寧窗(Hanning Window)、海明窗(Hamming Window)、布拉克曼窗(Blackman Window)等,不同的窗函數具有不同的特點,表現在主瓣旁瓣寬度,頻率識別精度及幅度識別精度等方面。圖1為Matlab仿真圖,分別為原始信號,原始信號加窗(海明窗)結果,原始信號做512點FFT結果,原始信號加窗后再做512點FFT結果,這4幅圖直觀形象地描述了時域信號做FFT后的頻域結果,以及原始信號是否加窗對FFT結果的影響。

2 FFT IP核

FFT IP核是高速執行的,參數可配置的FFT處理器,可以實現復數形式的FFT變換和IFFT變換。想要正確地使用FFT IP核,首先需要了解其引擎結構、數據流結構和關鍵管腳信號。

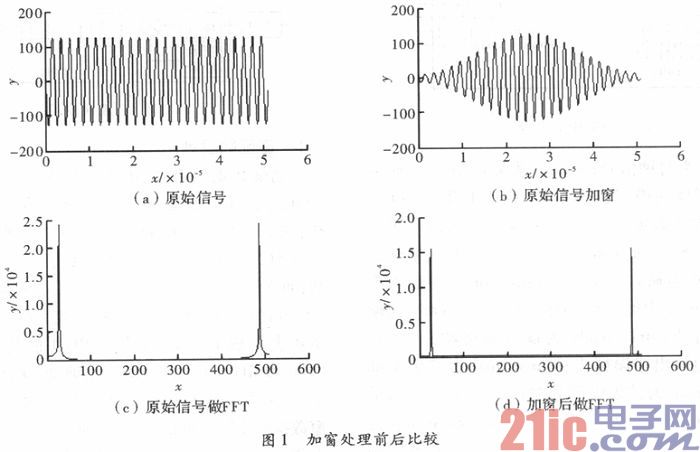

2.1 引擎結構

FFI IP核有兩種不同的引擎結構:四輸出和單輸出,結構如圖2(a)和圖2(b)所示。核心區別在于FFT蝶形處理器的吞吐量。一個時鐘周期內,四輸出結構可以計算出所有4個蝶形輸出,單輸出結構可以計算出一個蝶形輸出。

2.2 數據流結構

FFI IP核支持流、變量流、緩沖突發、突發4種數據流結構。流結構允許連續輸入數據,同時輸出連續的復數數據流。變量流產生一個與流結構類似的連續輸出數據流。緩沖突發結構需要存儲資源相對較少,但平均吞吐量也相應降低。突發結構的執行過程與緩沖突發結構類似,對于給定的參數設置,突發結構需要更少的存儲資源。

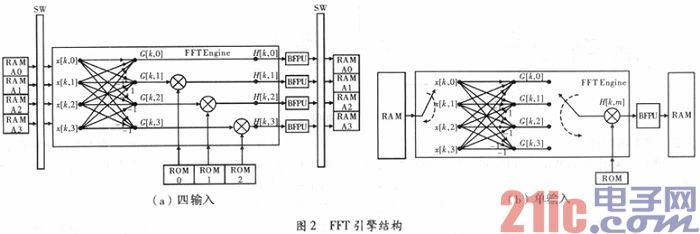

其中,clk為時鐘信號;reset_n為復位信號;inverse為FFT處理器變換模式選擇信號,選擇FFT或IFFF;sink_valid為輸入數據有效信號;sink_sop為輸入第一個數據標志信號;sink_eop為輸入最后一個數據標志信號;sink_real為輸入實部數據;sink_imag為輸入虛部數據;sink_error為輸入錯誤標志;source_ready為輸出等待狀態標志;sink_ready為輸入等待狀態標志;source_error為輸出錯誤標志;source_real為結果實部數據;source_imag為結果虛部數據;source_exp為結果補償系數;source_valid為結果有效信號;source_sop為

輸出第一個數據標志信號;source_eop為輸出最后一個數據標志信號。

3 方案設計

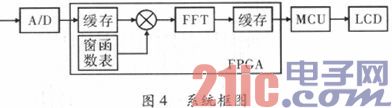

系統主要由三部分組成:A/D采集模塊、FPGA處理模塊及MCU運算顯示模塊,系統框圖如圖4所示。A/D采集外部信號數據,將其存入FPGA內部緩存RAM。當FFT輸入有效時,讀取緩存中的數據,同時與窗函數表中的對應系數做乘法運算,結果輸入FFT核中,FFT核處理結束后將數據存入緩存RAM中。單片機讀取緩存RAM中的結果數據,進行相應的模值計算,并通過LCD顯示結果頻譜圖形。該方案的核心在于窗函數與FFT運算核的設計與實現。

3.1 窗函數設計

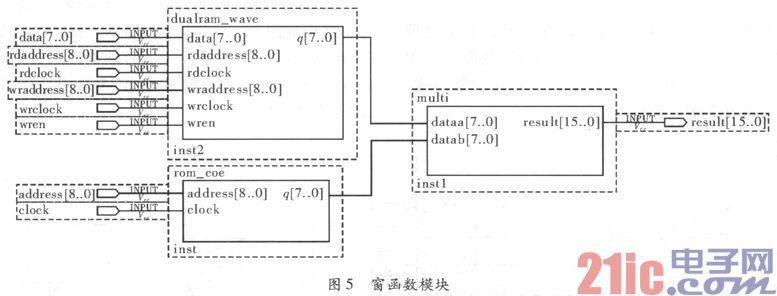

前端數據緩存采用雙口RAM核,深度512,位寬8 bit,存放A/D采集到的信號數據。窗函數表采用ROM核,深度512,位寬8 bit,存放窗函數數據。通過Matlab生成512點Hamming窗函數系數表,由于該數據為浮點數,而本設計中全部采用定點運算,故對窗函數系數進行256倍放大,將其變為定點整數,數據范圍為0~255。將系數表生成mif文件,作為ROM的初始化文件。該RAM和ROM采用同一套讀出地址,保證相應數據同步讀出,做乘法運算,得到16 bit結果數據。由于Hamming窗數據是實際數據的256倍,所以需要對乘法結果進行右移8位操作,得到8bit FFT輸入數據。設計模塊如圖5所示,該模塊實現了輸入信號數據的加窗處理。

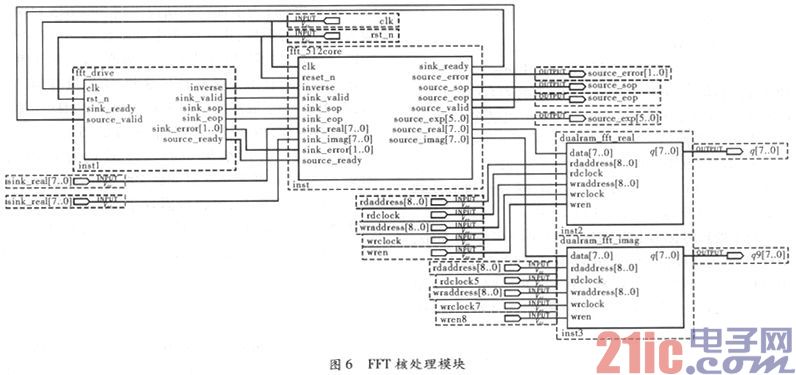

3.2 FFT核設計

FFT核采用MegaWizard FFT v11.1,變換點數選擇512,數據精度8 bit,引擎結構選擇單輸出結構,引擎數為1,I/O數據流結構選擇突發(Burst)結構。FFT輸出數據有3種:實部數據、虛部數據和補償指數數據。采用兩個雙口RAM核,深度均為512,寬度均為8 bit,分別存放

FFT核的實部結果數據和虛部結果數據。由于每512個FFT輸出數據,補償指數均相同,所以設置一個8 bit的寄存器存放補償指數即可。設計模塊如圖6所示,該模塊實現了加窗處理后的信號數據的快速傅里葉變換。

4 仿真與硬件驗證

4.1 系統仿真

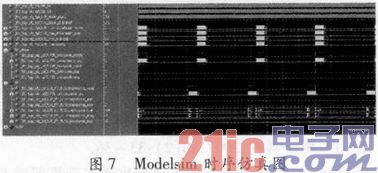

FPGA開發環境為QuartusII 11.1,仿真環境為Modelsiml0.0。仿真時,由Matlab生成波形數據mif文件,作為仿真測試數據文件存入波形緩存RAM中。通過Quartus II調用Modesim對測試工程進行仿真,仿真時序如圖7所示。經時序分析可知,工作時鐘頻率為100 MHz(period= 10 ns),每進行一次512點處理到全部輸出處理結果共耗時36.9μs。

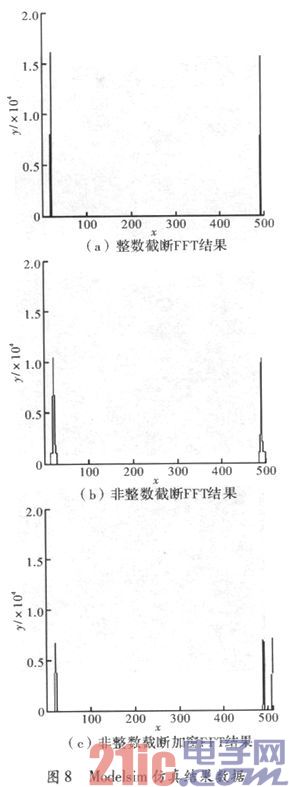

將仿真結果數據導入Matlab,得到結果由圖8(a)知,對信號周期整數倍截斷FFT處理后,得到單一的正確的頻譜圖;如圖8(b)知,對信號周期非整數倍截斷FFT處理后,頻譜出現嚴重泄露,且幅度值下降;如圖8(c)知,對信號周期非整數倍截斷,加窗后做FFT處理,頻譜泄露現象有明顯的改進,但幅度值因為加窗處理而相應下降。仿真結果表明,FFT系統設計正確,且加窗處理對信號周期非整數倍截斷導致的頻譜泄露問題有良好的改進效果。

4.2 硬件驗證

ADC選用ADS9238,它是一款高速高動態范圍A/D轉換器,12 bit,最高采樣時鐘達65 MSample·s-1。MCU選用c8051F120單片機,LCD選用ZLG320240K-FFSSWE-YBC,分辨率為320×240,可以滿足字符、漢字及圖形等各種顯示需求。FPGA選用Altera公司的Cyclone II EP2C8Q208 C8N,該芯片資源豐富,包含8256個LEs,36個4 kbit Block RAM,18個內部乘法器和208個I/O資源,并支持FFT IP核。

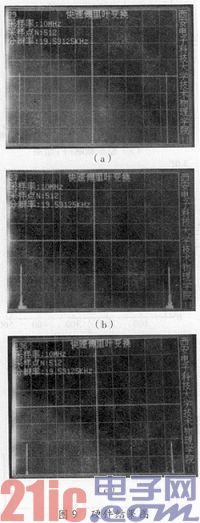

FFT處理時鐘為100 MHz,A/D采樣率為10 MHz,采樣點數為512,故頻譜分辨率f=10 MHz/512=19.531 kHz。當輸入信號為390.625 kHz時,512個采樣點表示20個信號周期;當輸入信號為400.390 kHz時,512個采樣點表示20.5個信號周期。在加窗和不加窗兩種情況下分別對頻率為390.625 kHz和400.390 kHz的正弦信號進行采樣,得到如圖9的結果。

圖9中(a)為不加窗的情況下對390.625 kHz的輸入信號進行采樣,由于512個點正好是20倍截斷,所以只在頻譜的第20個點有單一幅值,說明FFT系統工作正常。而且由于是整數倍截斷,結果沒有頻譜泄露;圖9(b)為不加窗的情況下對400.390 kHz的輸入信號進行采樣,由于512個點正好為20.5倍截斷,非整數倍截斷,所以結果中存在嚴重的頻譜泄露;圖9(c)為加窗的情況下對400.390 kHz的輸入信號進行采樣,可以看到,頻譜泄露現象得到較好的改善。硬件測試結果表明,FFT系統設計正確,且加窗處理對信號周期非整數倍截斷導致的頻譜泄露問題有良好的改進效果。

5 結束語

本文利用Altera公司的IP核設計了一種FFT系統,該方法設計簡單、資源利用率高、運算速度快,試驗證明具有良好性能。同時針對非整數倍周期截斷導致的頻譜泄露問題,提出了一種通過加窗改進的方法,經硬件平臺驗證,其改進效果明顯。由于加窗導致的幅值變化問題,本文尚未作詳細論證,有待進一步的研究。

評論