- 來自日本東京科學研究所(Science Tokyo)的一組研究人員 conceptualised 一種創新的 2.5D/3D 芯片集成方法,稱為 BBCube。傳統的系統級封裝(SiP)方法,其中半導體芯片使用焊點排列在二維平面(2D)上,存在尺寸相關的限制,需要開發新的芯片集成技術。為了高性能計算,研究人員通過采用 3D 堆疊計算架構開發了一種新型電源技術,該架構由直接堆疊的動態隨機存取存儲器上放置的處理單元組成,這是 3D 芯片封裝的重大進步。為了實現 BBCube,研究人員開發了涉及精確和高速鍵合技

- 關鍵字:

2.5D/3D封裝 工藝制程

- 來自日本東京科學研究所 (Science Tokyo) 的一組研究人員構思了一種名為 BBCube 的創新 2.5D/3D 芯片集成方法。傳統的系統級封裝 (SiP) 方法,即使用焊料凸塊將半導體芯片排列在二維平面 (2D) 中,具有與尺寸相關的限制,因此需要開發新型芯片集成技術。對于高性能計算,研究人員通過采用 3D 堆棧計算架構開發了一種新穎的電源技術,該架構由直接放置在動態隨機存取存儲器堆棧上方的處理單元組成,標志著 3D 芯片封裝的重大進步。為了實現 BBCube,研究人員開發了涉及精確和高速粘合

- 關鍵字:

2.5D/3D 芯片技術 半導體封裝

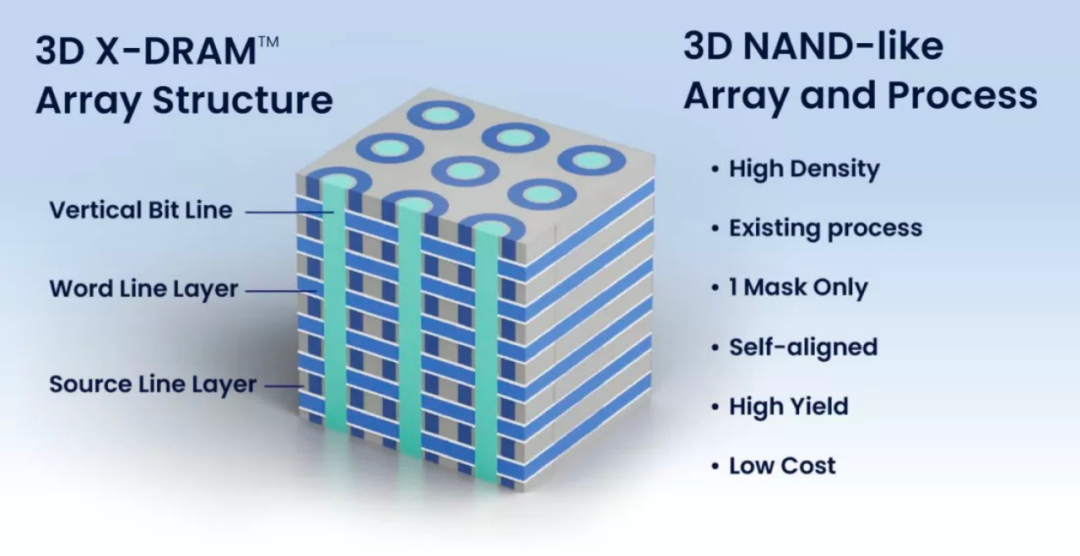

- 存儲設備研發公司Neo Semiconductor Inc.(加利福尼亞州圣何塞)推出了其3D-X-DRAM技術的銦-鎵-鋅-氧化物(IGZO)變體。3D-X-DRAM 于 2023 年首次發布。Neo 表示,它已經開發了一個晶體管、一個電容器 (1T1C) 和三個晶體管、零電容器 (3T0C) X-DRAM 單元,這些單元是可堆疊的。該公司表示,TCAD 仿真預測該技術能夠實現 10ns 的讀/寫速度和超過 450 秒的保持時間,芯片容量高達 512Gbit。這些設計的測試芯片預計將于 2026 年推出

- 關鍵字:

Neo Semiconductor IGZO 3D DRAM

- 12 月 6 日消息,博通當地時間昨日宣布推出行業首個 3.5D F2F 封裝技術 3.5D

XDSiP 平臺。3.5D XDSiP 可在單一封裝中集成超過 6000mm2 的硅芯片和多達 12 個 HBM 內存堆棧,可滿足大型 AI

芯片對高性能低功耗的需求。具體來看,博通的 3.5D XDSiP 在 2.5D 封裝之外還實現了上下兩層芯片頂部金屬層的直接連接(即 3D 混合銅鍵合),同時具有最小的電氣干擾和卓越的機械強度。這一“面對面”的連接方式相比傳統“面對背”式芯片垂直堆疊擁有 7 倍的信

- 關鍵字:

博通 3.5D F2F 封裝平臺 富士通 MONAKA 處理器

- 隨著半導體行業的快速發展,先進封裝技術成為了提升芯片性能和功能密度的關鍵。近年來,作為2.5D和3D封裝技術之間的一種結合方案,3.5D封裝技術逐漸走向前臺。什么是3.5D封裝技術3.5D封裝技術最簡單的理解就是3D+2.5D,通過將邏輯芯片堆疊并將它們分別粘合到其他組件共享的基板上,創造了一種新的架構。能夠縮短信號傳輸的距離,大幅提升處理速度,這對于人工智能和大數據應用尤為重要。不過,既然有了全新的名稱,必然要帶有新的技術加持 —— 混合鍵和技術(Hybrid Bonding)。混合鍵合技術的應用為3.

- 關鍵字:

封裝技術 TSV 中介層 3.5D

- ●? ?占用空間小,性能強勁●? ?緊湊便攜●? ?激光動平衡技術小型高性能復合軸承渦輪分子泵HiPace 10 Neo普發真空的新型HiPace 10 Neo渦輪分子泵是一款緊湊型真空泵。它便于集成在便攜式設備中,尤其是分析儀器行業。得益于普發真空的激光動平衡技術HiPace10 Neo 是該系列歷史上具有最小的噪音排放和極低的振動頻率的一款產品。普發真空產品經理亞歷山大·克魯特(Alexander Kreuter)表示:“作為真空技術的領先供

- 關鍵字:

Neo 渦輪分子泵 普發真空

- 芯原股份近日宣布低功耗?AIoT?芯片設計廠商炬芯科技股份有限公司(炬芯科技,?股票代碼:688049.SH)在其高集成度的雙模藍牙智能手表SoC? ATS3085S和ATS3089系列中采用了芯原低功耗且功能豐富的2.5D圖形處理器(GPU)IP。?炬芯科技的智能手表SoC ATS3085S和ATS3089系列擁有卓越的圖形顯示性能,采用2D+2.5D雙GPU硬件加速配置,支持JPEG硬件解碼,具有高幀率、低功耗等特點。該系列SoC以其高集成度,可實現單

- 關鍵字:

炬芯 智能手表 芯原 2.5D GPU IP

- 目前英偉達的H100等數據中心GPU都是由臺積電(TSMC)負責制造及封裝,SK海力士則供應HBM3芯片。不過人工智能(AI)的火熱程度顯然超出了大家的預期,導致臺積電的先進封裝產能吃緊。雖然臺積電不斷擴大2.5D封裝產能,以滿足英偉達不斷增長的需求,但是英偉達在過去數個月里,與多個供應商就2.5D封裝產能和價格進行談判,希望能夠分擔部分工作量。據The Elec報道,三星已經獲得了英偉達的2.5D封裝訂單。其高級封裝(AVP)團隊將向英偉達提供中間層,以及I-Cube封裝。I-Cube屬于三星自己開發的

- 關鍵字:

三星 英偉達 封裝 2.5D

- 月 8 日消息,據韓國電子行業媒體 TheElec 報道,三星電子成功拿下了英偉達的 2.5D

封裝訂單。消息人士透露,三星的先進封裝 (AVP) 團隊將為英偉達提供 Interposer(中間層)和 I-Cube,這是其自主研發的

2.5D 封裝技術,高帶寬內存 (HBM) 和 GPU 晶圓的生產將由其他公司負責。據IT之家了解,2.5D

封裝技術可以將多個芯片,例如 CPU、GPU、I / O 接口、HBM 等,水平放置于中間層上。臺積電將這種封裝技術稱為

CoWoS,而三星則稱之為

- 關鍵字:

三星 英偉達 AI 芯片 2.5D 封裝 訂單

- ●? ?Neo NPU可有效地處理來自任何主處理器的負載,單核可從 8 GOPS 擴展到 80 TOPS,多核可擴展到數百 TOPS●? ?AI IP可提供業界領先的 AI 性能和能效比,實現最佳 PPA 結果和性價比●? ?面向廣泛的設備端和邊緣應用,包括智能傳感器、物聯網、音頻/視覺、耳戴/可穿戴設備、移動視覺/語音 AI、AR/VR 和 ADAS●? ?全面、通用的 NeuroWeave SDK 可通過廣泛的 Caden

- 關鍵字:

Cadence Neo NPU IP NeuroWeave SDK

- 西門子數字化工業軟件近日推出Tessent Multi-die軟件解決方案,旨在幫助客戶加快和簡化基于2.5D和3D架構的新一代集成電路(IC)關鍵可測試性設計(DFT)。隨著市場對于更小巧、更節能和更高效能的IC需求日益提升,IC設計界也面臨著嚴苛挑戰。下一代組件正傾向于采用復雜的2.5D和3D架構,以垂直(3D IC)或并排(2.5D)方式連接多個晶粒,使其能夠作為單一組件運作。但是,這種做法為芯片測試帶來巨大的挑戰,因為大部分傳統的測試方法都是基于常規的2D流程。為了解決這些挑戰,西門子推出Tess

- 關鍵字:

西門子 2.5D 3D 可測試性設計

- 在燧原科技(燧原)發布云燧T10之際,燧原與格芯(GLOBALFOUNDRIES)近日共同宣布推出針對數據中心培訓的高性能深度學習加速卡解決方案,其核心“邃思”(DTU)基于格芯12LP?FinFET平臺及2.5D 封裝技術,為云端人工智能訓練平臺提供高算力、高能效比的數據處理。燧原的“邃思”(DTU)利用格芯12LP ?FinFET平臺擁有141億個晶體管,采用先進的2.5D封裝技術,支持PCIe 4.0接口和燧原 Smart Link高速互聯。支持CNN/RNN等各種網絡模型和豐富的數據類型

- 關鍵字:

FinFET 2.5D

neo-5d介紹

您好,目前還沒有人創建詞條neo-5d!

歡迎您創建該詞條,闡述對neo-5d的理解,并與今后在此搜索neo-5d的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473