基于ADSP-BF561的車輛輔助駕駛系統(tǒng)硬件設(shè)計(jì)方案

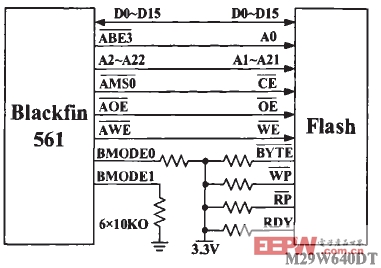

b)Flash

圖2存儲(chǔ)器連接

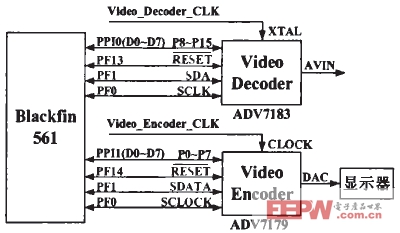

2.4并行輸入/輸出外圍接口電路

ADSP-BF561提供兩個(gè)可直接與并行A/D和D/A轉(zhuǎn)換器、符合ITU-601/656標(biāo)準(zhǔn)的視頻編碼和解碼器以及與其他通用外設(shè)連接的并行接13(PPI),每個(gè)PPI包括一個(gè)專用時(shí)鐘引腳,由時(shí)鐘電路產(chǎn)生。3個(gè)幀同步引腳和16個(gè)數(shù)據(jù)引腳。通過視頻解碼器ADV7183與ADSP-BF561的PPl0連接.視頻編碼器ADV7179與ADSP-BF561的PPll連接.從而實(shí)現(xiàn)車輛輔助駕駛系統(tǒng)中的環(huán)境感知傳感和人機(jī)界面功能.其連接如圖3所示。

圖3并行輸入/輸出連接

2.5 CAN接口電路

CAN(Controller Area Network)總線,即控制器局域網(wǎng)總線.是一種有效支持分布式控制或?qū)崟r(shí)控制的串行通信網(wǎng)絡(luò).目前已廣泛用于汽車等控制領(lǐng)域。利用ADSP-BF561處理器串行SPI總線接口單元與CAN控制器MCP2515芯片的無縫連接.通過對(duì)轉(zhuǎn)換芯片內(nèi)部寄存器的操作.并通過CAN接收器SN65230芯片實(shí)現(xiàn)數(shù)據(jù)的收發(fā)。

3 軟件及實(shí)驗(yàn)分析

系統(tǒng)的硬件設(shè)計(jì)是后續(xù)代碼編寫和算法實(shí)現(xiàn)的基礎(chǔ).因此完成上述系統(tǒng)的硬件開發(fā)后,編寫底層驅(qū)動(dòng)模塊和系統(tǒng)軟件框架,并把視覺處理算法進(jìn)行相關(guān)移植。ADI公司提供一套完整的軟件開發(fā)工具Visual DSP++,利用Visual DsP++項(xiàng)目管理環(huán)境,程序員可以方便的開發(fā)和調(diào)試應(yīng)用程序,同時(shí)開發(fā)軟件的編譯器能有效地將C,C十+代碼轉(zhuǎn)換為Blackfin DSP的匯編代碼.采集結(jié)果如圖4(a)所示。

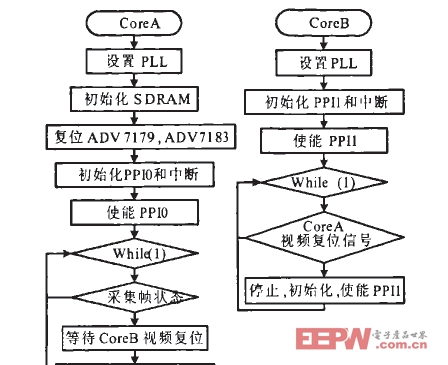

ADSP-BF561為對(duì)稱雙核處理器,因此在程序編寫的時(shí)采用不同內(nèi)核處理不同工作,并根據(jù)硬件接口進(jìn)行調(diào)試軟件的編寫.CoreA工作主要包括設(shè)置時(shí)鐘頻率、初始化SDRAM控制器、初始化視頻編解碼器、初始化PPl0和中斷、使能PPIO.以ITU656模式進(jìn)行獲取,獲取到的幀存放在SDRAM中:CoreB工作主要包括設(shè)置時(shí)鐘頻率、初始化PPI1和中斷、使能PPI1,以通用輸出模式執(zhí)行視頻輸出,軟件流程如圖4(b)所示。

a) 采集界面

b)軟件流程

圖4采集界面及流程圖

4 結(jié)論

本系統(tǒng)采用了ADI公司功能強(qiáng)大的媒體處理器ADSP-BF561.在完成最小系統(tǒng)和擴(kuò)展功能硬件開發(fā)后.可以在該硬件平臺(tái)上方便地進(jìn)行代碼和算法開發(fā).視覺處理系統(tǒng)在整個(gè)系統(tǒng)設(shè)計(jì)中起著重要作用.其硬件設(shè)計(jì)的成功完成.能夠縮短開發(fā)周期.降低開發(fā)成本并且為車輛輔助駕駛系統(tǒng)的開發(fā)打下堅(jiān)實(shí)基礎(chǔ)。

本文作者創(chuàng)新點(diǎn):利用數(shù)字信號(hào)處理器ADSP-BF561進(jìn)行車輛輔助駕駛系統(tǒng)硬件設(shè)計(jì),實(shí)現(xiàn)視頻實(shí)時(shí)采集與顯示.為車輛輔助駕駛視覺處理算法開發(fā)提供實(shí)驗(yàn)平臺(tái)。

評(píng)論