基于ADSP-BF561的車輛輔助駕駛系統(tǒng)硬件設(shè)計

有源品振信號質(zhì)量好、比較穩(wěn)定、連接簡單和不需要復(fù)雜的配置電路。因此ADSP-BF561系統(tǒng)輸入時鐘采用30MHz的外部有源品振然后通過其內(nèi)部鎖相環(huán)PLL把頻率進(jìn)行相應(yīng)的倍頻作為ADSP-BF561的總線頻率和SDRAM的時鐘頻率,同時由于并行輸入,輸出外圍接13和視頻編解碼芯片的時鐘需要,需要把27MHz有源晶振通過IDT2305分成4路輸出。

2.3存儲擴(kuò)展電路

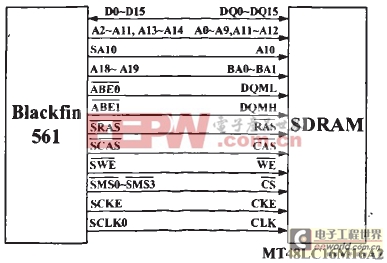

SDRAM是同步尋址存儲器,由塊、行和列組成.全部讀店操作鎖定于一個處理器源時鐘,一旦處理器對SDRAM進(jìn)行初始化。該存儲器必須不斷更新,以確保能保持它的狀態(tài).SDRAM的時鐘速率可變,工業(yè)上最常用的是PCI00和PCI33,最高時鐘頻率分別為100MHz和133MHz。ADSP-BF561擁有SDRAM控制器(SDC)與SDRAM的無縫連接,其連接如圖2(a)所示,系統(tǒng)采用MT48LCl6M16A2,容量為32MHz,最高頻率為133MHz。

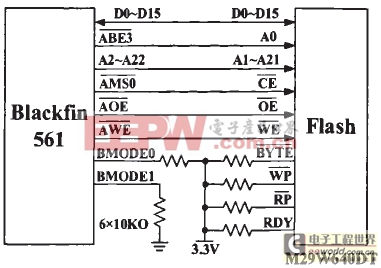

ADSP-BF561具有異步存儲器控制器(AMc),與SDRAM控制器共享數(shù)據(jù)和地址引腳。當(dāng)上電復(fù)位或者軟件初始化復(fù)位后.處理器采樣復(fù)位配置寄存器BMODE引腳,執(zhí)行引導(dǎo)功能。系統(tǒng)采用BMODEIO為由8116位Flash引導(dǎo)模式,并選用NORFLASH作為引導(dǎo)代碼存儲器,所選芯片為容量8MB的M29W640DT.其連接方式如圖2(b)所示。

a) SDRAM

b)Flash

圖2存儲器連接

評論