從4004到core i7:處理器的進(jìn)化史(3)-4-第一次加速

現(xiàn)在加入流水線。為了將每個環(huán)節(jié)分割開來,我們需要在環(huán)節(jié)之間加入寄存器以隔離相鄰的環(huán)節(jié),獲得獨(dú)立的輸入、輸出。不妨假設(shè)在相鄰環(huán)節(jié)之間插入只一個寄存器。其具有自己的時間約束t_c,q(寄存器從輸入到輸出的傳輸延時)和t_su(建立時間,這常常和具體的電路結(jié)構(gòu)有關(guān))。為了保證正確性,需要有:

本文引用地址:http://www.104case.com/article/233547.htm由于我們將整個電路分割成了很多個很小的部分,因此max(t_pd)一般要遠(yuǎn)遠(yuǎn)小于t_pd,logic,也就是說,我們可以大大提升時鐘頻率,這與前面的敘述是一致的。

然而上面的t_c,q和t_su卻給我們提了一個醒:

主頻的提升并非沒有代價,它實(shí)際上是以一條指令完整執(zhí)行的時間(latency)的延長(它現(xiàn)在需要通過很多級寄存器了)來換取吞吐量(throughput,即單位時間內(nèi)流經(jīng)某一級的指令數(shù)量)的提升。

在指令流連續(xù)時,一切都很美好;但是一旦指令流中斷(最典型的當(dāng)然是branch),引入pipeline的額外開銷就顯著地體現(xiàn)出來了。這里我再自己寫一個公式:

T_sum=T_latency+N*T_min,pipe

其中T_sum是執(zhí)行一段很長很長的指令流的總用時(第一條IF到最后一條WB),N是指令數(shù)。這樣,我們得到了一種衡量性能的方法:

t_avg=T_latency/N+T_min,pipe

不難想象,當(dāng)N很小時,很長的pipleline帶來的巨大的latency將會讓平均指令執(zhí)行時間t_avg變得很難看。

事實(shí)上還有一個限制主頻瘋狂提升的因素。記得嗎,那就是我前面說過的功耗!

正因為以上的兩個因素,intel雖然曾經(jīng)將netburst的流水線做到了28級,頻率提高到3.8GHz,甚至差一點(diǎn)就發(fā)布了4GHz的Pentium 4,卻最終冷靜了下來,不再通過越來越深的pipeline不顧一切地提升時鐘頻率了。

作為參照,core架構(gòu)的流水線僅14級。

pipeline并不是萬靈藥,我們需要另外的加速方法。

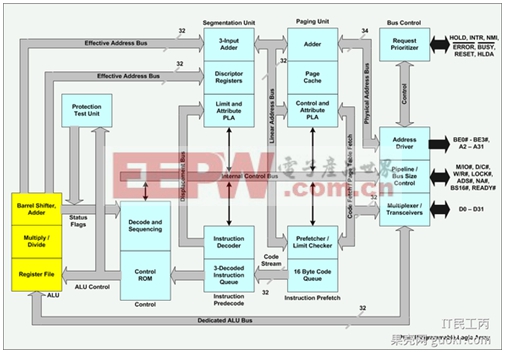

說完了pipeline,你應(yīng)該就能看懂這張386的圖了:

Pipeline is everywhere!!

評論