用系統(tǒng)級方法實現(xiàn)SiP設(shè)計

本文詳細描述了SiP的各種系統(tǒng)級設(shè)計方法和各自的應(yīng)用領(lǐng)域,包括堆疊式芯片結(jié)構(gòu)、相鄰解決方案、芯片疊加技術(shù)(CoC)以及三維通孔堆疊式結(jié)構(gòu)。

蜂窩電話和數(shù)碼相機的迅速普及以及它們對小型半導(dǎo)體封裝尺寸的要求使得系統(tǒng)級封裝(SiP)解決方案變得越來越流行。但SiP的優(yōu)勢不僅僅在尺寸方面。因為每個功能芯片都可以單獨開發(fā),而系統(tǒng)級芯片(SoC)必須作為大型的單芯片設(shè)計來開發(fā),因此SiP具有比SoC更快的開發(fā)速度和更低的開發(fā)成本。

早在2001年,SiP解決方案就建立在了功能芯片的基礎(chǔ)上,這些功能芯片針對單芯片封裝經(jīng)過驗證、設(shè)計和嘗試。但由于這些功能芯片原本是為芯片級封裝而設(shè)計,這樣的解決方案在SiP開發(fā)中會產(chǎn)生嚴(yán)重的問題。因為當(dāng)兩個芯片進行堆疊時,它們的焊點經(jīng)常無法對齊。有時對應(yīng)的焊點會位于這兩個芯片相對的兩側(cè),此時需要通過插入器進行信號布線。

通過多層封裝插入器完成的信號連接有很大的缺陷。由于走線長度的增加,信號完整性會降低。另外,封裝插入器的成本也很高。為了克服這些缺點,設(shè)計工程師開發(fā)出了焊點位置適合更短走線連接的SiP芯片。例如,存儲器接口焊點放在邏輯芯片的上側(cè)和下側(cè),連接到外部引腳的信號焊點放在左右兩側(cè)。如果存儲器芯片是長方形的,可以將焊點移到長度較短的兩條邊上。然后就可以沿一個方向?qū)⑦壿嬓酒痛鎯ζ餍酒询B起來,將存儲器芯片的短邊連接到具有存儲器接口焊點的邏輯芯片的上下兩側(cè)。

另外,當(dāng)需要整合用不同晶圓工藝和不同代的加工工藝生產(chǎn)出來的芯片時,廣泛使用相鄰SiP封裝技術(shù)。例如,在汽車應(yīng)用中的相鄰SiP就可能包含了采用邏輯晶圓制造工藝生產(chǎn)的信號處理器和采用模擬晶圓制造工藝生產(chǎn)的實際驅(qū)動器芯片。在這種情況下,可以用新一代晶圓工藝改善信號處理器的性能和成本,而驅(qū)動器芯片仍保持使用穩(wěn)定的晶圓工藝,因為它需要長期工作在12V電壓下。由于新一代工藝不能處理更高的電壓,這時SiP就成了這種芯片組合的最佳候選方法。

|

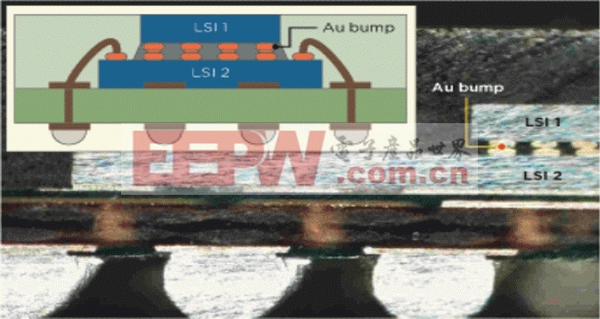

圖:為了滿足移動設(shè)備的性能、功耗和尺寸的要求,芯片疊加(CoC)方法不再采用金線連接,而是采用凸塊連接方式。 |

同時提供模擬和數(shù)字功能的封裝解決方案還會引起另外一個問題。如果模擬芯片包含信號輸入接收器或輸出驅(qū)動器功能,那么信號、幅度和極性首先要受數(shù)字芯片控制,然后通過模擬芯片。這種組合通常是一種串行連接,通常模擬芯片尺寸要小于數(shù)字芯片。如果這些整合使用堆疊式芯片結(jié)構(gòu),那么模擬芯片應(yīng)放在數(shù)字芯片上面。

信號會從數(shù)字芯片焊點出來,通過與封裝插入器相連接的信號線經(jīng)過模擬芯片,這樣信號就可以在模擬和數(shù)字芯片間傳輸。此時相鄰SiP是更好的選擇。

芯片疊加技術(shù)

相鄰SiP解決方案看起來很象以前的微型多芯片模塊,但原始單芯片性能的提高要求增加子芯片。SiP中芯片堆疊的想法最初來自于縮小整體封裝尺寸的要求。可以將數(shù)碼相機當(dāng)作近來同時要求高性能和小尺寸的典型應(yīng)用例子。目前流行的數(shù)碼相機通常具有500萬像素傳感器,但幾年前典型的傳感器只有100萬像素,也即這幾年來要求的性能提高了五倍,同時要求降低所需功耗,確保目前數(shù)字相機有更長的電池壽命。為了滿足這些看似矛盾的要求,許多公司開發(fā)出了芯片疊加(CoC)技術(shù)。采用這種技術(shù)后,在邏輯和存儲器芯片之間不再采用金線連接,而是采用凸塊連接方式。

由于邏輯芯片和存儲器之間沒有金線連接,因此信號數(shù)據(jù)傳輸速度能夠變得更快。CoC方法也能降低功耗,并具有專用I/O緩沖。一般的雙倍數(shù)據(jù)速率存儲器總線上每個信號管腳焊點要求2.5V信號擺幅、50mA最大電流和125mW最大功率。當(dāng)使用專用I/O緩沖時,與傳統(tǒng)130nm供電電壓相同的1.2V信號擺幅將成為合適的選擇。

由于I/O緩沖負(fù)載只是點到點連接,因此可能只使用十分之一的電流。最終,工作頻率可以提高五倍,電壓降低一半,電流降到十分之一,功耗只有四分之一。另外一個額外好處是芯片尺寸將變得更小。

隨著用于邏輯芯片的新一代晶圓工藝的發(fā)展以及對更多存儲容量需求的增長,存儲器芯片尺寸看起來將超過邏輯芯片尺寸。這意味著將沒有裸露的焊點區(qū)域可以用來建立外部管腳用的連接。超先進電子技術(shù)協(xié)會(ASAET)定義的三維通孔堆疊結(jié)構(gòu)可以解決這個問題。由于采用這種技術(shù)后會使邏輯芯片和堆疊存儲器芯片在三維通孔基底中建立很短的連接路徑,因此即使小型邏輯芯片也能夠在不降低信號完整性的前提下處理很大的存儲容量。

這一領(lǐng)域的開發(fā)工作才剛剛展開,新方法和新技術(shù)層出不窮。例如,設(shè)計師可以選擇與存儲器芯片一樣大小的邏輯芯片,并使用三維通孔基底將它與存儲器芯片堆疊在一起。通過這樣重復(fù)邏輯芯片和堆疊存儲器芯片結(jié)構(gòu),設(shè)計師最終可以創(chuàng)建一個具有"巨大存儲容量"的SiP。

SiP解決方案有多種形式,包括旨在縮小外形尺寸的堆疊式芯片結(jié)構(gòu),適合I/O端接功能芯片的相鄰解決方案,適合低功耗高頻率工作的CoC以及用于大容量存儲器的三維通孔堆疊式結(jié)構(gòu)。

過去,SiP的主要優(yōu)勢在于很短的開發(fā)交付時間,但最近的可行性研究表明,SiP還能提供與SoC相似的性能。另外,SiP允許不同晶圓工藝的芯片存在于同一解決方案中,因此使得SiP不僅只是一種封裝,而且是一個真正的系統(tǒng)。

評論