基于FPGA原型的GPS基帶驗證系統設計與實現

3 FPGA驗證平臺設計和實現

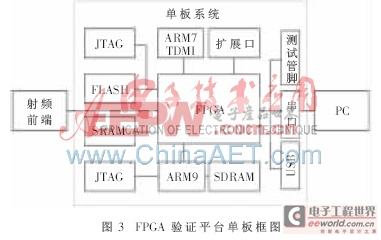

FPGA驗證平臺的結構如圖3所示。

FPGA芯片采用Altera公司Stratix III系列的EP3SL-150F1152C3,ARM7CPU采用ARM7TDMI的驗證測試芯片,ARM9芯片采用Samsung的S3C2410芯片。

由于ARM7內核無法移植,所以采用外接的ARM7TDMI測試芯片作為CPU,同時電路板上集成了一塊ARM9芯片。因此該平臺也可用于基于ARM9內核的SOC驗證平臺,并且板上預留的擴展接口可以再接一塊ARM9芯片,可用于雙核的開發。

基帶芯片其他部分都位于FPGA芯片中。編譯后的電路通過FPGA旁邊的JTAG接口下載到FPGA芯片中,通過ARM旁邊的JTAG接口進行軟件下載和調試。軟件調試工具使用ADS1.2。信號可以通過RS232串口或者USB接口與上位機進行通訊。

4 驗證中的問題分析和解決

從ASIC到FPGA的移植需要根據實際情況做一些調整。在該系統中,采用ARM7TDMI測試芯片的CPU時鐘由FPGA內部產生,經由電路板送到ARM7芯片,由于板級布線延時,FPGA內部時鐘和ARM7時鐘在相位上不再保持同步,由此造成時序混亂。因此,在FPGA輸出時鐘到ARM7之前要做相位調整,以補償在板級線路的延時。

FPGA驗證也有不足之處。

首先,調試困難,由于EDA工具不夠完善,所以缺乏有效的調試手段。示波器和邏輯分析儀作為主要的調試工具,在問題的定位上給驗證人員提出了更高的要求;雖然目前的EDA軟件集成了內部的在線邏輯分析儀,但是在使用上仍然有缺陷。協助調試方法主要有2種:(1)軟件仿真和硬件模擬結合,當硬件調試很難對問題定位時,可以將代碼編譯成二進制文件保存到ROM中,在軟件平臺上運行程序,提高信號的可觀察性。(2)在基帶結構中增加測試電路,對關鍵信號進行監視,當出現問題時可利用測試電路所保存的數據進行分析。

紅外熱像儀相關文章:紅外熱像儀原理

評論