基于FPGA的DDFS與DDWS兩種實(shí)現(xiàn)方式

DDS(Direct Digital Freqiaency Synthesizers)廣泛應(yīng)用于雷達(dá)系統(tǒng)、數(shù)字通信、電子對(duì)抗、電子測(cè)量等民用軍用設(shè)備中。它是隨著半導(dǎo)體技術(shù)和數(shù)字技術(shù)的快速發(fā)展而發(fā)展起來的新型的頻率合成技術(shù),與傳統(tǒng)的VCO+PLL的模擬方式產(chǎn)生所需頻率相比,DDS技術(shù)具有頻率分辨率高,相位噪聲低,帶寬較寬,頻譜純度好等優(yōu)點(diǎn)。這些技術(shù)指標(biāo)在一個(gè)系統(tǒng)中是至關(guān)重要的,決定著一個(gè)系統(tǒng)的成敗。

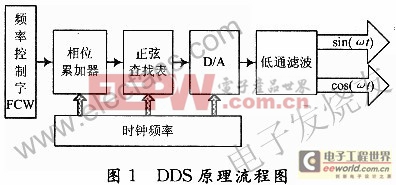

1 DDS的基本原理

1.1 頻率合成方式的基本原理

DDFS是根據(jù)余弦函數(shù)相位和幅值的對(duì)應(yīng)關(guān)系,從相位出發(fā),由不同的相位給出不同的電壓幅值,再經(jīng)過D/A變換和濾波最后得到一定頻率和調(diào)頻率的模擬信號(hào)。由此可見,DDS有很多功能模塊組成,如圖1所示。

若相位累加器有N位,時(shí)鐘頻率為fclk,頻率控制字為FCW。N位的相位累加器可以對(duì)時(shí)鐘頻率進(jìn)行2N分頻,所以DDS的精度可以達(dá)到:

![]()

頻率控制字是用來控制累加器的步進(jìn)的,累加器的步進(jìn)為![]() 。假設(shè)初始的相位偏移△φ=0,則經(jīng)過N個(gè)時(shí)鐘周期后相位累加器的輸出θ=2π*FCW*N*(1/2N)。在相位步進(jìn)△0時(shí),完成2π的相位變化即為完成一個(gè)輸出周期,所以20/△θ*Tclk=T0,即:

。假設(shè)初始的相位偏移△φ=0,則經(jīng)過N個(gè)時(shí)鐘周期后相位累加器的輸出θ=2π*FCW*N*(1/2N)。在相位步進(jìn)△0時(shí),完成2π的相位變化即為完成一個(gè)輸出周期,所以20/△θ*Tclk=T0,即:

![]()

可見調(diào)節(jié)FCW可以任意地按照要求改變輸出頻率,這就達(dá)到了頻率合成的目的。

1.2 直讀方式DDS的原理

直讀法(DDWS)工作流程是,把所需要的DDS的波形,直接用Matlab抽樣量化,然后把量化的數(shù)據(jù)直接存儲(chǔ)到FPGA的BlockRAM中,再在時(shí)鐘頻率的控制下直接從BlockRAM中讀取數(shù)據(jù),D/A后輸出原來波形。

評(píng)論